[原创] EDA软件性能提升一小步,芯片设计迈出一大步

2021-07-03

14:00:46

来源: 半导体行业观察

当下IC设计的趋势主要朝着以下几个方面发展:首先是Time to market 的时间越缩越短,要让想法更快的变成芯片,尽快推向市场;然后是现在的设计和验证越来越复杂,这就需要庞大的算力;再就是软硬件协同的方法和现象越来越普遍,软件堆栈发展速度越来越快;而超过60%的工作都来自软件,大部分基于IP。

软件越来越成为IC设计成功与否的关键

。

在见证了涉及数据中心服务器、网络产品和智能手机制造商的客户对其验证和数字设计解决方案的强烈需求后,为了应对呈指数级上升的系统设计复杂度和上市时间的压力,EDA巨头Cadence最近推出了系统动力双剑Palladium Z2和Protium X2。双剑合璧能够为IC设计提供怎样的动力呢?

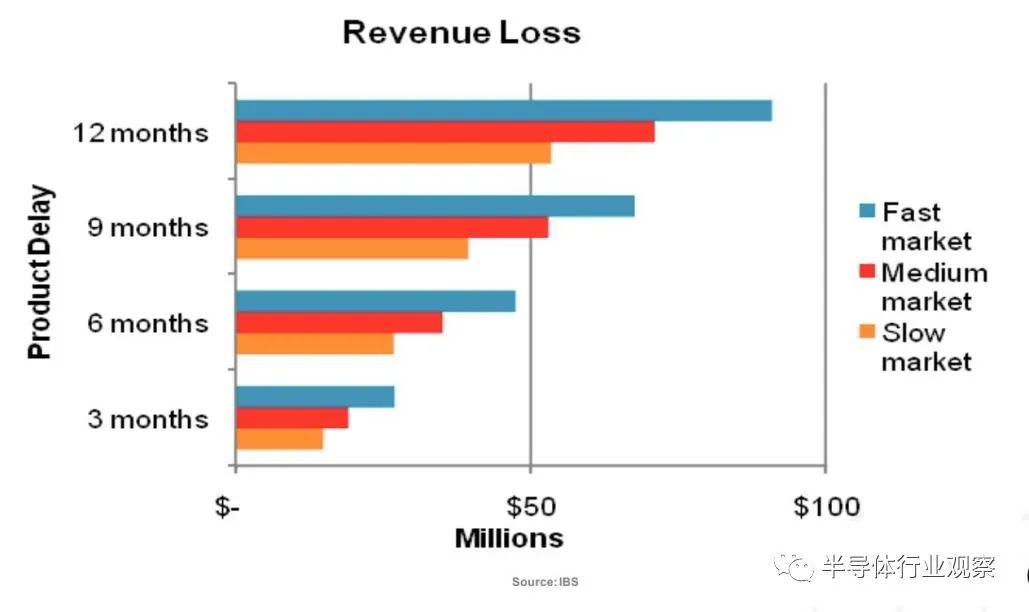

为什么说软件成为IC设计成功与否的关键?因为软件主导着芯片的开发成本和进度,软件也是成功销售芯片的必要条件,而延迟软件交付会延迟最终的市场收益(如下图所示)。所以Cadence认为,尽早开始软件开发是至关重要的,这样硅前硬件可以与软件一起验证。

如果能在芯片投入流片之前,将最终的软件与芯片结合起来,进行完整的验证,充分地把系统带起来。这样不仅可以保证流片能够成功,而且最终设计出的芯片在能耗、功效以及效能等方面会更符合你的需求。其逻辑就是把软件跟硬件协同的运作或仿真早一点能够达成。

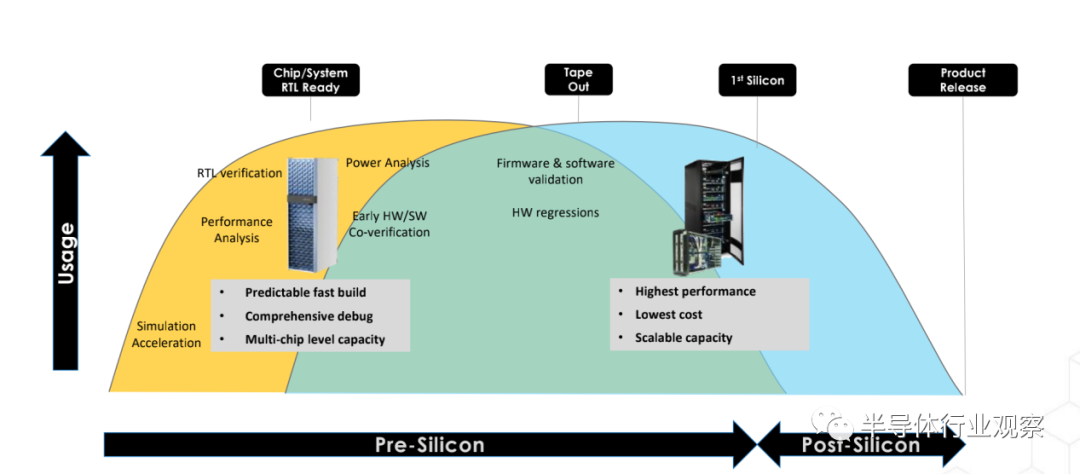

在这过程中就需要仿真加速和原型验证,但两者的关注点有所不同:仿真加速主要是“Debug你的芯片设计”,原型验证则是“Debug你的软件”。

具体来看,仿真加速专注的是Debug里的硬件—暨芯片或系统,例如能每天晚上重新构建新的RTL bug修复;当然不再只专注IP,重要的是SoC和子系统的容量要够大;同时还要进行快速和完整的调试,不但能进行完整的跟踪,还能在运行时就能够调试控件。

而原型验证最重要的一个要素就是高性能,当下的软件调试需要更长的模拟运行。原型验证也需要SoC集成,因为软件环境越来越多地需要从SoC级别设定和考虑。反而构建时间和调试显得没那么重要,如果设计稳定的话,每1-2周重新构建一次即可。

那么,在何时、何地、使用何种验证呢?当然是

在正确的时间,在正确的使用场景和工作中,使用正确的工具!

这个要怎么理解呢?Cadence公司亚太区系统解决方案资深总监张永专认为,在项目的不同时间节点所使用的工具是不一样的。在前期RTL Code Verification这段时间,包括功耗、性能以及编译调试的分析,会用仿真加速的方式。而当你的设计大概90%、80%都已经成熟的时候,软件团队需要介入进来的时候,此时就会慢慢地将设计迁移到原型验证这样一个平台,软件工程师就可以把你的软件在上面做,到最后芯片流片之前,会做所谓的进入系统的验证,叫System Signoff,通过System Signoff,基本上所有你要构建的软件,在还没流片之前,就已经全部都把系统归纳起来。这样操作下来,芯片的每次流片成功率将大大提升。

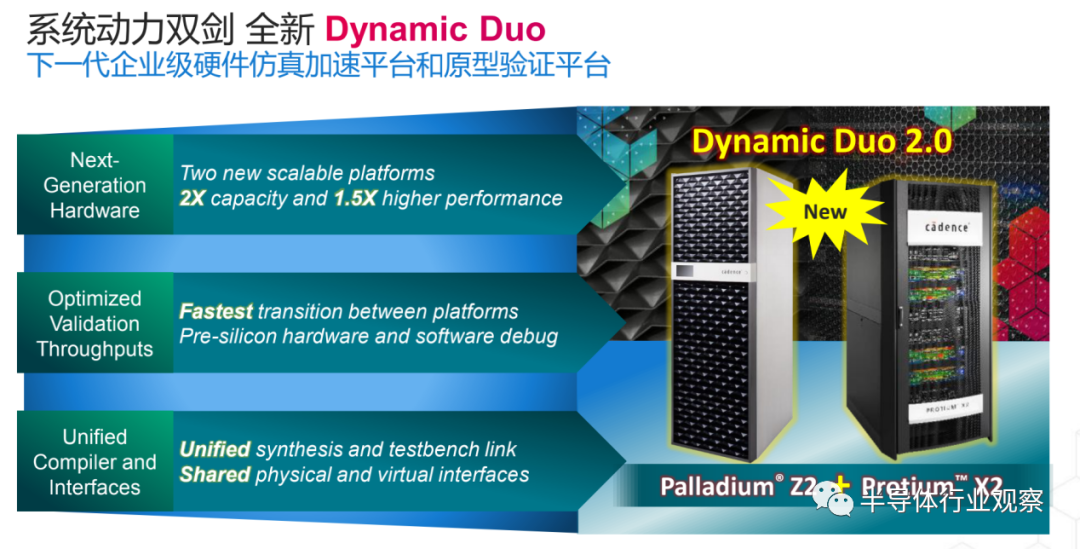

面对上述这样的需求,Cadence推出了 Palladium Z2 企业级硬件仿真加速系统和Protium X2 企业级原型验证系统。此双系统无缝集成统一的编译器和外设接口,双剑合璧,被称为系统动力双剑(dynamic duo)。基于Cadence原有的Palladium Z1和Protium X1产品,新一代系统为当前数十亿门规模的片上系统(SoC)设计提供最佳的硅前硬件纠错效率和最高的软件调试吞吐率。

新产品Palladium Z2 平台和Protium X2 平台基于下一代硬件仿真核心处理器和Xilinx UltraScale+ VU19P FPGA,

将为客户带来2倍容量提升和1.5倍性能提升

,以更少的时间为大规模芯片验证完成更多次数的迭代。此外,模块化编译技术也突破性地应用在两个系统中,使得100亿门的SoC编译可以在Palladium Z2 系统10小时内即可完成,Protium X2系统也仅需不到24小时就可以完成。

张永专强调到:“

不要小看所谓的1.5倍的效率提升,想象一下,如果一个项目周期原来是12个月,可能之后4个月就做完了。所以应用这个产品,对于设计公司来说,可以是提升竞争力是非常关键的武器和工具

。”这真的是EDA软件效率提升一小步,就能让芯片设计迈出一大步。

那么新一代的系统动力双剑究竟能为客户带来哪些突破性提升呢?这就要看看实际采用客户的感受。

采用Cadence Palladium Z2 和 Protium X2平台提升性能。英伟达能够按时完成对最复杂GPU和SoC设计的全面验证。也为AMD在开发最具挑战的SoC设计时,提供了优化自身的左移策略的机会。Arm已经在最新设计上实现了超过50%的性能提升和2倍的容量增加,为其提供了验证下一代IP和产品所需的强大的硅前验证能力。此外,Xilinx和Cadence密切合作,确保Cadence软件前端与Xilinx Vivado设计套件后端无缝协作,实现最佳性能和容量优势。

Palladium Z2 & Protium X2 动力双剑主要解决那些为最先进应用程序设计的人所面临的挑战,包括移动、消费和超大规模计算设计。基于无缝集成的流程、统一的纠错、通用的虚拟和物理接口以及跨系统的测试平台内容,该动力双剑组合可以实现从硬件仿真到原型验证的快速设计迁移和测试。

据了解,Palladium Z2 和 Protium X2 平台于 2021 年第二季度全面上市。

据张永专介绍,Cadence现在的整体战略思维是集中在智能系统设计战略。他们在EDA工具中引入了人工智能学习的基本方式,例如在验证的部分,工具可以学习客户好的回归测试或项目验证,进而用机器学习的方式加速验证的收验;再如在后端学习客户的绕线的基本方法,以此来进一步优化。不仅如此,Cadence还开放了人工智能的Database,客户可以共用这个数据库,享受到人工智能和机器学习的好处。

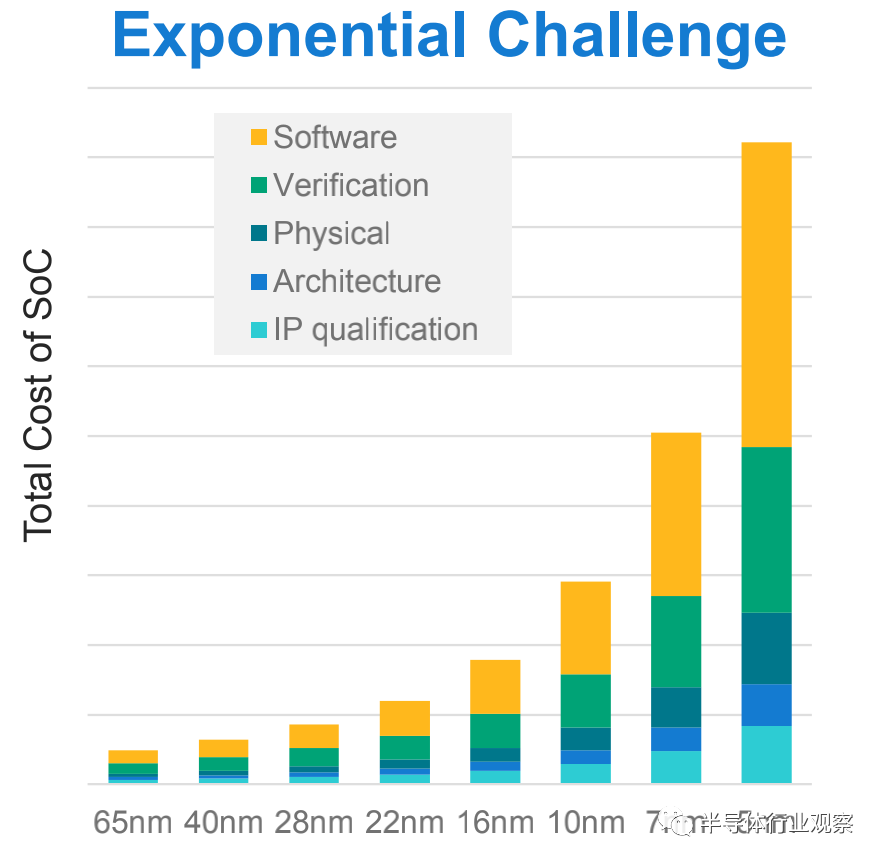

除了智能系统设计,验证也是SoC很重要的一部分。对于不同的工艺节点,尤其是来到先进工艺,验证所需要的花费越来越多,Cadence希望能尽量保证用户所花的每一分钱、工程师每天所能找到的Bug都最大化。所以Cadence的数字验证策略就要确保验证的速度。

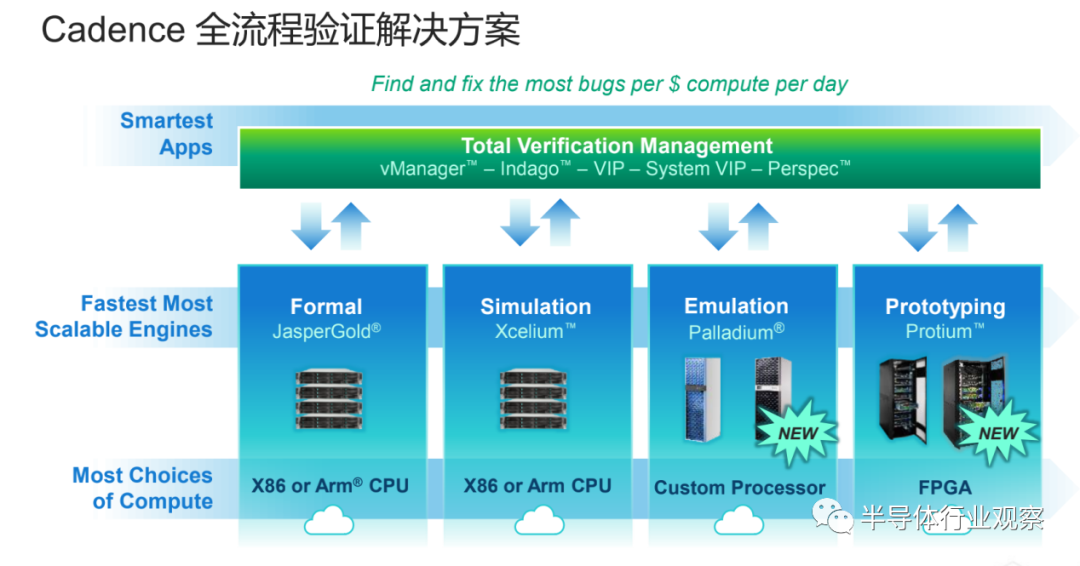

对此,Cadence提出了全流程的验证解决方案,它主要包括四个关键的引擎:形式验证引擎(JasperGold)、Xcelium™仿真平台、Protium跟Palladium(系统动力双剑)。通过这四个引擎可以快速的验证设计,能把验证相关的大数据全部收集到Verification Management整个完整的验证管理系统vManager中。这样就可以让项目管理、工程师,乃至整个公司的工程团队都能知道验证的进度以及验证的缺陷点跟人力的缺口,整个项目很快就可以收验。在这其中,还有人工学习的方式在大数据中定位错误。整体下来,保证了验证的效率最大化。

尤其要说一下系统动力双剑的优势,它可以说是在行业内拥有最快的编译速度,每两个小时可以编译25亿门,10小时内能编译100多亿门。而且无需重新编译即可快速触发。再就是Protium的软件验证速度很快,是3到5倍Palladium的速度,可以在几天内就可以从Palladium迁移到原型验证的平台。

目前在整个业界大概有90%的客户都应用了Palladium,它有最高的硅前硬件调试生产率。当下在数据中心可能需要20亿门,GPU大约需要15亿门,而Palladium Z2 平台可从作业规模小至 800万门扩展到大至184亿门,充分满足当前厂商的需求,而且像这样一个机架可以同时容纳144个用户在上面上线使用。同时Palladium拥有最全面的接口组合,如在线仿真,虚拟化,内存模型

Cadence是一个以计算型软件为核心的公司,并且专注于研发,8800个工程师在3年开发了超过20个新产品,以满足电子和半导体公司不断增长的需求。此次系统动力双剑Palladium Z2和Protium X2的发布,可以说是芯片设计企业缩短项目开发时长、提升自身竞争力的一个非常有力的武器。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2725内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|MLCC|英伟达|模拟芯片

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie