硅芯科技亮相CSPT 2025:以全流程EDA平台推动2.5D/3D先进封装协同创新

2025-11-01

22:36:00

来源: 李晨光

点击

10月28日,在CSPT 2025中国半导体封装测试技术与市场大会上,珠海硅芯科技有限公司赵毅博士以“打通关键路径:2.5D/3D先进封装EDA平台串联设计与制造协同创新”为主题发表主题演讲,从行业趋势、技术挑战与客户需求出发,系统介绍了其自主研发的3Sheng Integration 2.5D/3D Chiplet EDA平台,并在大会上举行了该平台发布仪式,致力于为行业提供“设计-仿真-测试-制造”全流程协同的解决方案,展现了国产EDA工具在先进封装领域的突破性进展。

硅芯科技核心负责人赵毅博士在CSPT 2025主题演讲

硅芯科技核心负责人赵毅博士在CSPT 2025主题演讲

在当前后摩尔时代,随着HPC、AI等大算力应用对芯片性能需求持续攀升,传统芯片面临“内存墙、功耗墙、面积墙”等多重瓶颈制约:

· 内存墙:存储速度滞后算力增长,传统存算分离架构带宽不足;

· 功耗墙:英伟达GPU功耗已达700W,未来HPC芯片功率将突破1000W,逼近功率密度极限;

· 面积墙:单Die尺寸受光罩限制无法继续增加,难以满足大算力需求。

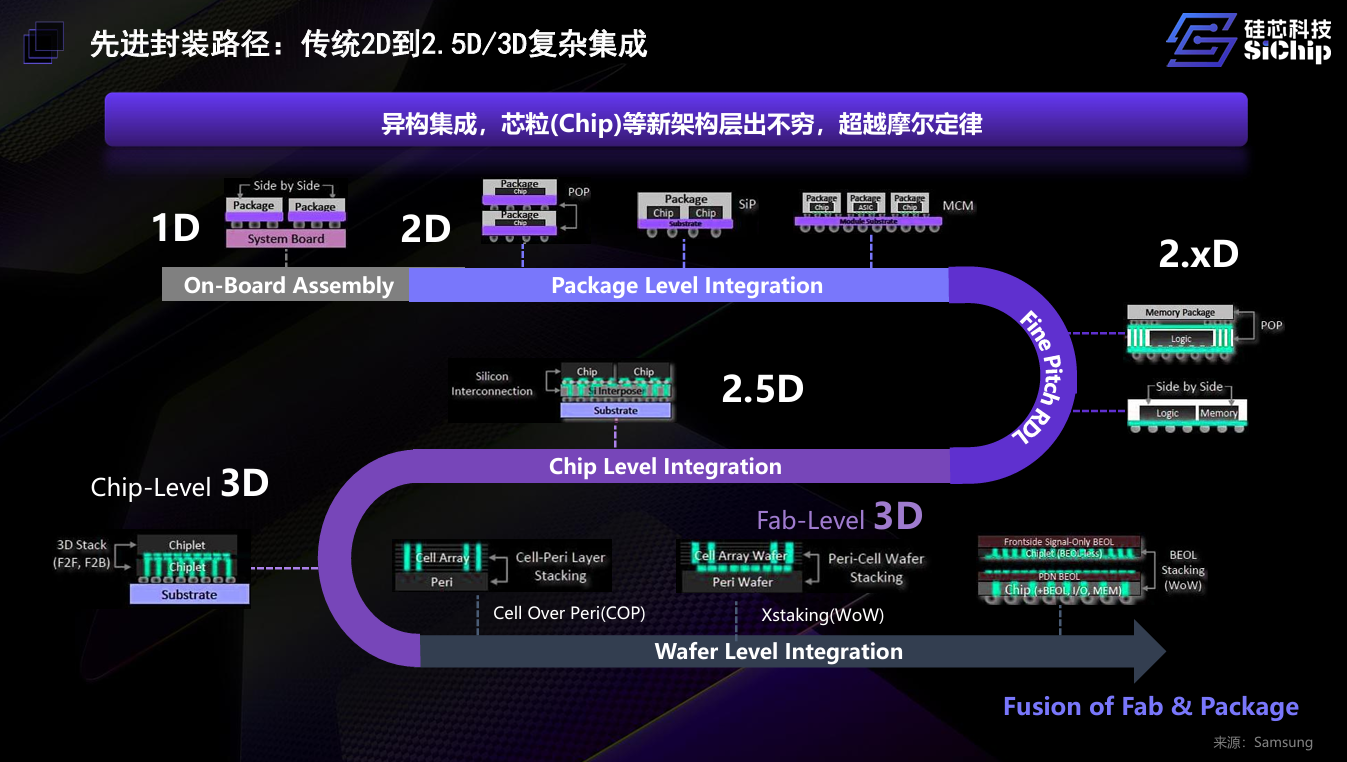

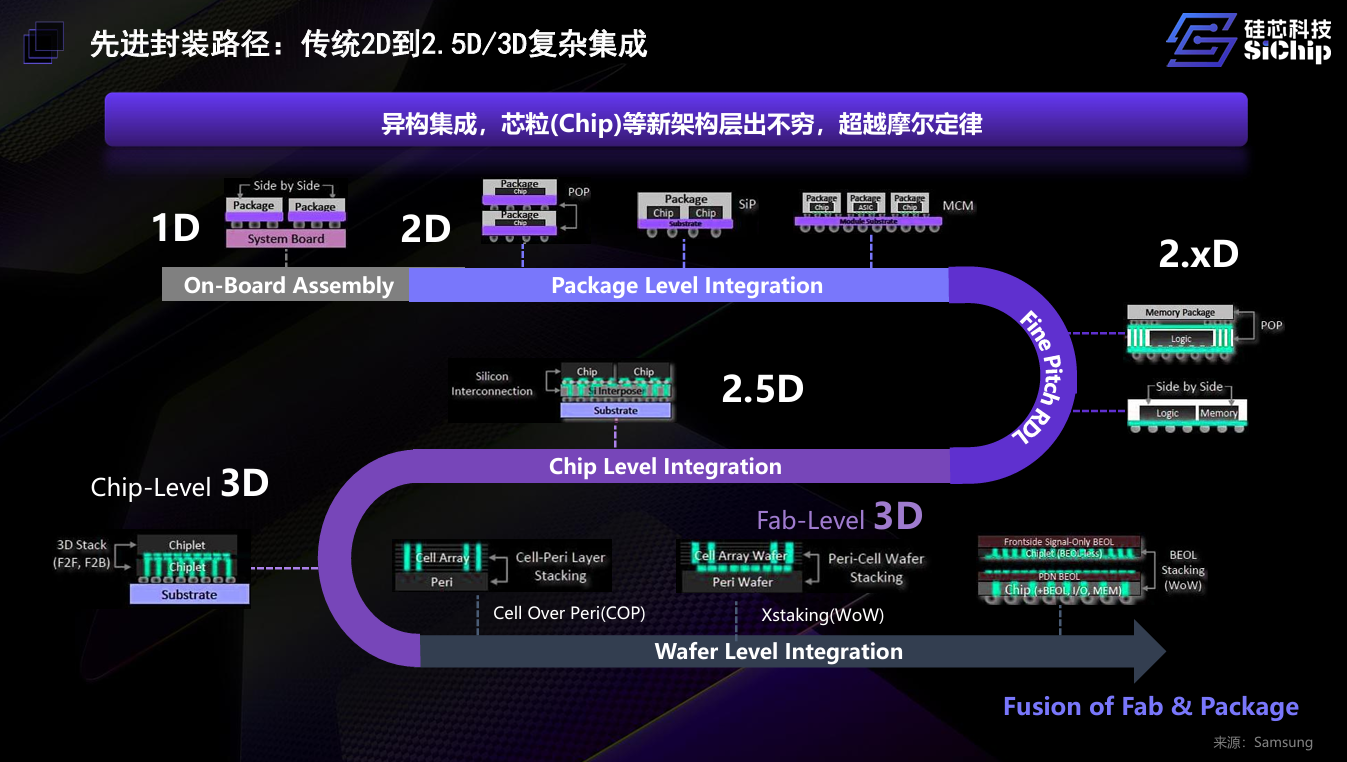

在此背景下,先进封装正在从2D平面集成向2.5D/3D复杂集成等方向演进,通过异构集成、Chiplet架构与先进封装技术,成为突破瓶颈的关键路径。

但先进封装在带来产品创新优势的同时,随之而来的是设计复杂度呈指数级上升,对EDA工具提出了前所未有的挑战。

据介绍,传统2D芯片EDA工具因缺乏3D堆叠设计能力、多物理场分析模块及跨域协同机制,已无法满足当前行业需求,传统EDA工具重构成为行业刚需,需从单一环节工具升级为“全流程协同平台”,覆盖从系统级架构规划到封装签核的全链路,实现多维度协同与高可靠性保障等。

针对行业需求,硅芯科技推出3Sheng Integration 2.5D/3D先进封装EDA应用生态平台,以“架构设计-物理实现-测试容错-分析仿真-验证签核”等五大中心为核心,构建覆盖全流程的2.5D/3D Chiplet设计闭环:

· 架构设计中心:支持系统级建模、成本预估与架构探索,实现Chiplet划分与D2D互连规划;

· 物理设计中心:具备3D布局布线、TSV-微凸点协同规划、热驱动布线以及中介层-RDL联合设计等能力,支持Chiplet-Interposer-Package协同设计,解决传统工具碎片化设计问题;

· 测试容错中心:支持多Die DFT、系统级连通性检查与容错机制,兼容IEEE 1838等标准;

· 分析仿真中心:集成信号完整性、电源完整性、电热耦合等多物理场仿真,形成“电热力磁”多物理场耦合分析能力,实现设计-仿真闭环迭代;

· 多Chiplet集成验证中心:提供Multi-die LVS/DRC/STA等签核能力,支持硅中介层开路/短路检测、微凸点间距合规性验证,确保设计与制造参数匹配。。

综合来看,凭借上述几大核心能力,该平台的核心优势体现在多个方面,包括性能-成本-可测试性的协同优化,支持CoWoS、玻璃基板、硅桥、3D堆叠等多种先进封装工艺,打通设计-制造数据流,推动Chiplet的标准化与复用等,旨在破解先进封装行业痛点问题,加速AI、数据中心等大算力芯片的研发与落地。

正如硅芯科技所强调的,3Sheng Integration不仅是一套EDA工具集合,更是一个协同设计与制造的应用生态平台,通过标准化芯粒库、跨工艺协同设计,推动先进封装产业协同发展,助力国内半导体企业在AI、HPC等领域的算力突破。

据赵毅博士介绍,硅芯科技团队自2008年起便前瞻性地布局3D IC设计方法学研究,是全球首批投身于2.5D/3D堆叠芯片领域的开拓团队,这一深厚的技术积淀为其3Sheng Integration平台奠定了坚实基础,并已成功在多个行业客户中实现落地应用。

正是基于对技术路径与产业需求的深刻洞察,硅芯科技在演讲中指出,2.5D/3D堆叠芯片已不仅是单纯的技术趋势,更是驱动产业发展的时代所向。

面向未来,硅芯科技将持续深化3Sheng平台的生态融合,联动设计、制造、封测等上下游企业,构建“EDA-芯片-制造-系统应用”的全栈闭环生态,助力中国先进封装产业突破技术封锁,实现从跟随到并跑乃至引领的跨越。

在CSPT 2025大会现场,硅芯科技还举办了“3 Sheng Integration 2.5D/3D先进封装EDA应用生态平台”启动发布仪式,标志着国产EDA在突破先进封装设计瓶颈、构建协同创新生态方面迈出了坚实一步。

硅芯科技核心负责人赵毅博士在CSPT 2025主题演讲

硅芯科技核心负责人赵毅博士在CSPT 2025主题演讲先进封装成芯片算力突破关键,EDA工具面临重构

在当前后摩尔时代,随着HPC、AI等大算力应用对芯片性能需求持续攀升,传统芯片面临“内存墙、功耗墙、面积墙”等多重瓶颈制约:

· 内存墙:存储速度滞后算力增长,传统存算分离架构带宽不足;

· 功耗墙:英伟达GPU功耗已达700W,未来HPC芯片功率将突破1000W,逼近功率密度极限;

· 面积墙:单Die尺寸受光罩限制无法继续增加,难以满足大算力需求。

在此背景下,先进封装正在从2D平面集成向2.5D/3D复杂集成等方向演进,通过异构集成、Chiplet架构与先进封装技术,成为突破瓶颈的关键路径。

但先进封装在带来产品创新优势的同时,随之而来的是设计复杂度呈指数级上升,对EDA工具提出了前所未有的挑战。

据介绍,传统2D芯片EDA工具因缺乏3D堆叠设计能力、多物理场分析模块及跨域协同机制,已无法满足当前行业需求,传统EDA工具重构成为行业刚需,需从单一环节工具升级为“全流程协同平台”,覆盖从系统级架构规划到封装签核的全链路,实现多维度协同与高可靠性保障等。

3Sheng Integration平台:五大中心构建完整EDA生态

针对行业需求,硅芯科技推出3Sheng Integration 2.5D/3D先进封装EDA应用生态平台,以“架构设计-物理实现-测试容错-分析仿真-验证签核”等五大中心为核心,构建覆盖全流程的2.5D/3D Chiplet设计闭环:

· 架构设计中心:支持系统级建模、成本预估与架构探索,实现Chiplet划分与D2D互连规划;

· 物理设计中心:具备3D布局布线、TSV-微凸点协同规划、热驱动布线以及中介层-RDL联合设计等能力,支持Chiplet-Interposer-Package协同设计,解决传统工具碎片化设计问题;

· 测试容错中心:支持多Die DFT、系统级连通性检查与容错机制,兼容IEEE 1838等标准;

· 分析仿真中心:集成信号完整性、电源完整性、电热耦合等多物理场仿真,形成“电热力磁”多物理场耦合分析能力,实现设计-仿真闭环迭代;

· 多Chiplet集成验证中心:提供Multi-die LVS/DRC/STA等签核能力,支持硅中介层开路/短路检测、微凸点间距合规性验证,确保设计与制造参数匹配。。

综合来看,凭借上述几大核心能力,该平台的核心优势体现在多个方面,包括性能-成本-可测试性的协同优化,支持CoWoS、玻璃基板、硅桥、3D堆叠等多种先进封装工艺,打通设计-制造数据流,推动Chiplet的标准化与复用等,旨在破解先进封装行业痛点问题,加速AI、数据中心等大算力芯片的研发与落地。

正如硅芯科技所强调的,3Sheng Integration不仅是一套EDA工具集合,更是一个协同设计与制造的应用生态平台,通过标准化芯粒库、跨工艺协同设计,推动先进封装产业协同发展,助力国内半导体企业在AI、HPC等领域的算力突破。

据赵毅博士介绍,硅芯科技团队自2008年起便前瞻性地布局3D IC设计方法学研究,是全球首批投身于2.5D/3D堆叠芯片领域的开拓团队,这一深厚的技术积淀为其3Sheng Integration平台奠定了坚实基础,并已成功在多个行业客户中实现落地应用。

正是基于对技术路径与产业需求的深刻洞察,硅芯科技在演讲中指出,2.5D/3D堆叠芯片已不仅是单纯的技术趋势,更是驱动产业发展的时代所向。

面向未来,硅芯科技将持续深化3Sheng平台的生态融合,联动设计、制造、封测等上下游企业,构建“EDA-芯片-制造-系统应用”的全栈闭环生态,助力中国先进封装产业突破技术封锁,实现从跟随到并跑乃至引领的跨越。

在CSPT 2025大会现场,硅芯科技还举办了“3 Sheng Integration 2.5D/3D先进封装EDA应用生态平台”启动发布仪式,标志着国产EDA在突破先进封装设计瓶颈、构建协同创新生态方面迈出了坚实一步。

责任编辑:chenguang

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻