来源:内容由半导体行业观察(ID:icbank)编译自「

tomshardware

」,谢谢。

一段时间以来,半导体公司一直在探索摆脱传统单片 GPU 芯片设计的方法,寻找能够实现更好的性能扩展同时将生产成本保持在合理水平的方法。Nvidia 推动事物向前发展的最新方法是使用硅通孔 (TSV) 技术和增强的功率传输方法引入3D 芯片堆叠。这听起来类似于我们已经从 AMD、英特尔和台积电那里听说过的技术,但也存在一些差异。

我们已经知道英伟达一直在计划摆脱单片芯片设计。该公司一直在积极探索使用不同封装技术获得更高性能的方法,最新的方法是使用多芯片模块 (MCM) 来构建具有持续性能可扩展性的 GPU。

早在 2017 年,英伟达就在国际计算机体系结构研讨会 (ISCA) 上展示了其 MCM-GPU 设计。英伟达计划使用多个逻辑芯片来互连大量内核,并开发具有持续性能改进的新 GPU,同时管理成本。随着 GPU 芯片越来越大,它们的成本呈指数级增长,因此制作一些相互连接的较小芯片是更具成本效益的解决方案。MCM-GPU 封装方法解决了这个问题,因为它连接多个芯片,从而提供巨大的性能提升作为回报。

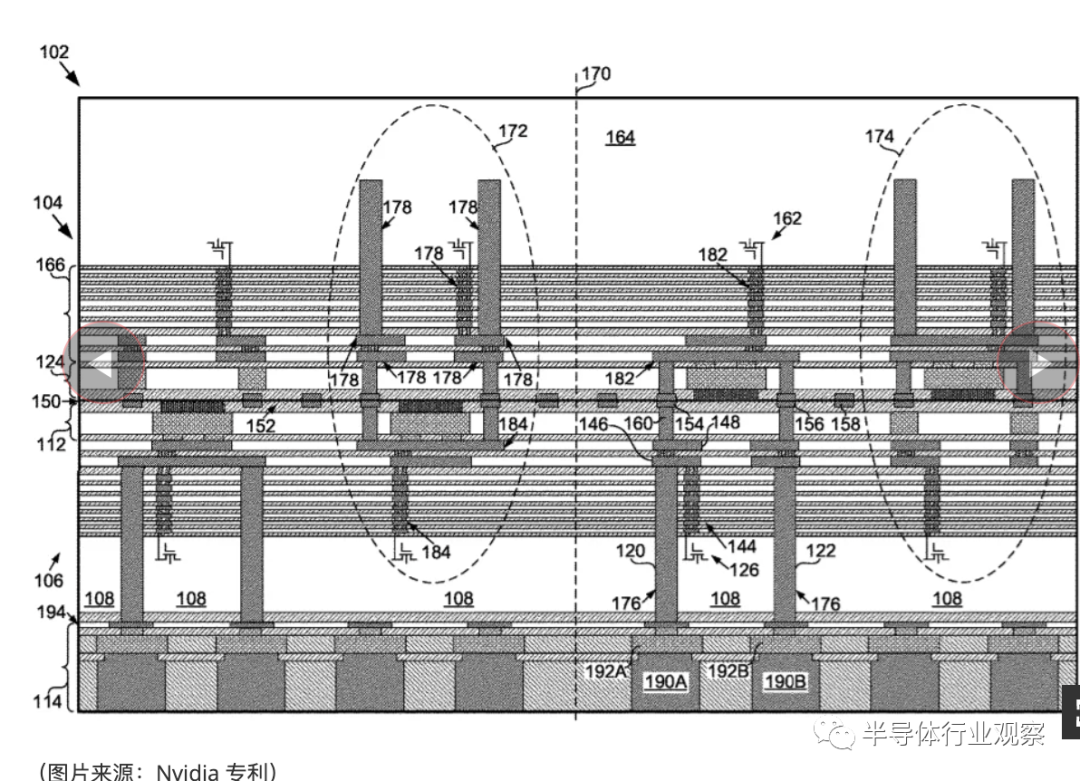

芯片设计不限于二维缩放,而这正是英伟达今天所获得的专利。Nvidia 提出了“使用扩展 TSV 增强功率传输的面对面die”,提出了半导体die的 3D 堆叠,并特别说明了使用超长硅通孔 (TSV) 增强功率传输。

这种设置的工作方式是首先使用芯片表面上的探针垫测试基础芯片。之后,在第一个die的表面上形成界面层,覆盖在已经存在的探针焊盘上。最后,取出第二个die并将其安装在界面层上,将die间接口的焊盘连接到其他die上的互补连接。这创建了裸片的面对面安装,3D 芯片诞生了。

Nvidia 的专利专注于使用超长 TSV 增强电力传输。当像这样将芯片堆叠在一起时,您可以连接从逻辑(处理核心)到内存的任何东西。通常,连接内存不需要太多电力,因此提及增强的电力传输使我们得出结论,Nvidia 计划执行处理内核的堆叠,为 3D 处理器创建面向计算的方法。

当然,申请专利并不意味着实际产品必须使用专利技术。公司经常为发明申请专利以防止他人这样做,或者只是作为未来产品的占位符。无论哪种情况,我们都已经知道 MCM-GPU 方法即将到来,像 Hopper 这样的一些下一代 GPU 架构可以利用 3D 芯片堆叠的优势来获得竞争优势。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2805内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!