技术文章 | 高速DAC JESD204接口接收机物理层压力测试(上)

2026-03-19

13:52:58

来源: 互联网

点击

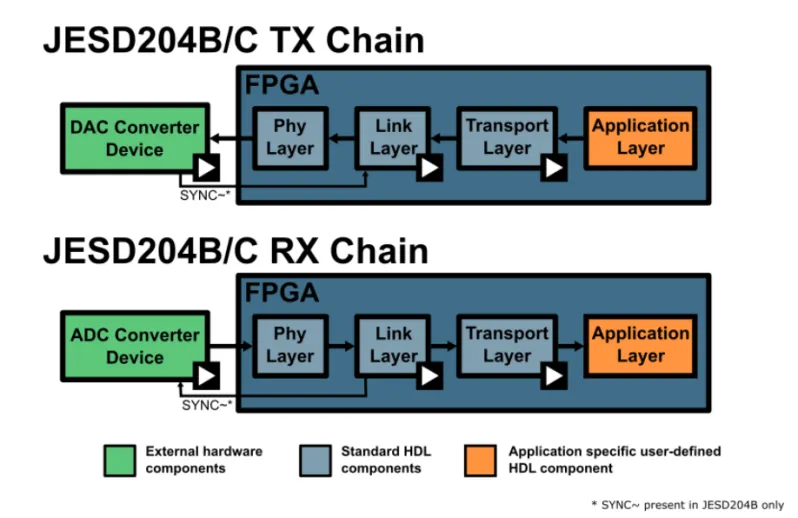

随着无线通信向5G/6G演进以及雷达系统向宽带多模发展,高速数模转换器(DAC)的采样率已突破GSPS量级,数据接口从传统的并行LVDS全面转向高速串行JESD204B/C/D标准。在雷达,电子侦察(ESM)与干扰吊舱中,宽带接收机前端的 ADC/DAC 会在极恶劣的信噪比(SNR)下工作。伴随半导体发热以及无界热噪声会严重污染基带高速数据接口,传统的“连通性”测试已无法满足高可靠性芯片的设计需求,必须引入包含抖动注入(Jitter Injection)的压力测试(Stress Test)来摸底芯片的物理层余量。

本文深入探讨了JESD204C/D标准的物理层特性,结合中星联华科技SL3000系列误码仪的五大核心优势——高级抖动注入、通道间相位微调、高级自定义码型支持,0.5G-32G连续速率覆盖,以及信号完整性损伤板模拟真实恶劣环境, 插损板模拟标准要求的MR/LR插损场景,详细阐述了如何构建高保真的DAC接收机压力测试环境。文章重点分析了如何利用PJ注入模拟电源噪声与系统干扰,彻底评估DAC的时钟恢复(CDR)鲁棒性及最终的模拟输出性能,为提升国产高端DAC芯片的产品化可靠性提供实践指导。

图1 SL3000系列误码仪

一、 高速数据转换器接口的演进与挑战

1.1. 从LVDS到JESD204C/D的跨越

在过去十年中,数据转换器(ADC/DAC)的分辨率和采样率呈指数级增长。采用传统的并行CMOS或LVDS接口,意味着需要数百个I/O引脚,这在PCB布线密度、封装成本以及通道间时序对齐(Skew)方面都是不可接受的。

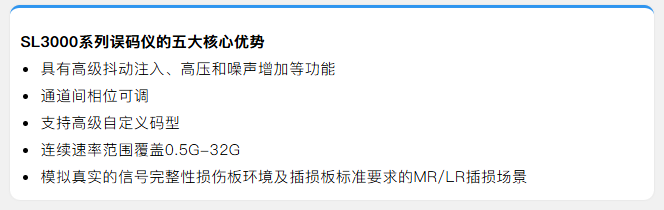

JEDEC固态技术协会推出的JESD204标准旨在解决这一瓶颈。

JESD204B:引入了确定性延迟(Deterministic Latency),通过Subclass 1(基于SYSREF)实现多芯片同步,最高速率达到12.5 Gbps,采用8b/10b编码。

JESD204C:为了提高传输效率,引入了64b/66b编码,降低了编码开销(从20%降至3%),单通道速率提升至32 Gbps。物理层定义了从Class A到Class C的多种类别,以适应不同长度的信道损耗。

图2 典型DAC和FPGA的应用框图实例

图3 JESD要求的不同速率

1.2. 高速DAC接收机(RX)面临的物理层测试挑战

在JESD204链路中,DAC芯片充当接收机(RX)的角色,FPGA或ASIC充当发射机(TX)。随着速率迈向32 Gbps,物理层面临信号完整性的挑战:

信道损耗(Insertion Loss):PCB走线在高频下的介质损耗和集肤效应导致信号眼图闭合。DAC接收端必须具备强大的连续时间线性均衡(CTLE)和判决反馈均衡(DFE)能力。

抖动(Jitter):在数十Gbps速率下,单位间隔(UI)仅为30ps左右。来自参考时钟的相位噪声、电源纹波引入的周期性抖动(PJ)、以及热噪声引入的随机抖动(RJ),都会压缩采样窗口,导致误码。

失真和噪声:在超过25Gbps的串扰和噪声更加严重,影响RX接收机的余量。

传统的“完美眼图”测试无法体现电子战设备在干扰压制下的鲁棒性,仅在理想条件下测试DAC“能工作”是远远不够的。标准要求必须在测试阶段引入压力测试,人为恶化输入信号质量,探测芯片在极限条件下的生存能力(余量)。

二、 JESD204C/D 物理层接收机测试

2.1. 接收机抖动容限(Jitter Tolerance, JTOL)测试

DAC内部集成了时钟数据恢复(CDR)电路,用于从高速串行流中提取采样时钟。CDR本质上是一个低通滤波器,它能跟踪低频抖动,但无法跟踪高频抖动。如果在CDR带宽之外存在过大的抖动,就会导致采样错误,进而不仅产生数字误码。

SL3000应用方案:

- 测试搭建:将SL3000的PPG输出连接至DAC的JESD输入端。DAC配置为通过SPI/I2C读取内部误码计数器(Error Counter),或将解帧后的数据环回至BERT的ED(若支持)。

- 基准测试:设置目标速率(如12.5 Gbps),不加抖动,调整SL3000的输出摆幅和预加重,确保DAC无误码锁定。

高级抖动注入(关键步骤):

- 利用SL3000的抖动注入功能,扫描SJ和PJ频率,从1KHz级别一直扫描至40MHz。

- 通过观察DAC在哪个抖动频率下开始出现误码或失锁,可以精确反推DAC内部CDR的环路带宽。SL3000支持的高频PJ注入能力在此处无可替代,因为很多电源噪声和时钟耦合干扰harmonics恰好落在10MHz-40MHz区间。

2.2. 接收机均衡能力与眼图灵敏度测试

JESD204C定义了不同等级的信道损耗(如Class C-R支持高损耗)。DAC接收端必须通过CTLE/DFE张开闭合的眼图。

SL3000应用方案:

- 最小输入幅度测试:利用SL3000输出幅度的连续可调特性,逐渐降低差分摆幅(例如从800mV降至200mV),测试DAC的输入灵敏度。

- 模拟长信道:在SL3000与DAC之间串入不同长度的ISI插损板,迫使DAC内部的CTLE/DFE全速工作。

通过上述测试方法,可以对DAC接收机在抖动、信道损耗及输入幅度等多维条件下的性能进行系统性验证,从而全面评估其物理层设计的鲁棒性与性能余量。

在实际工程中,这类测试不仅需要覆盖宽频段抖动扫描、多种信道损耗条件,还涉及复杂的信号质量调控与环境模拟,对测试系统的能力提出了极高要求。

围绕上述测试需求,下篇我们将针对JESD204C/D DAC测试中的关键需求,详述中星联华SL3000系列误码仪测试方法的工程实现与实例,剖析SL3000系列为何会成为JESD204C/D DAC测试的理想平台。

精彩预告

后续将针对JESD204C/D DAC测试中的关键需求,详述中星联华SL3000系列误码仪测试方法的工程实现与实例。

END

中星联华科技(Sinolink Technologies)成立于2009年,长期从事高频率、高速率、大带宽、宽频带测试测量技术研发,为卫星通信、雷达、复杂电磁环境等传统应用领域及5G移动通信、高速互连等新兴行业提供稳定可靠、性能卓越的专属测试测量工具。

聚焦成就专业,创新服务应用。深度理解行业应用,依托传统测试测量理论和技术,协同行业领军精英共同致力于改善测试工具的实用性、便捷性和经济性,帮助工程师将更多时间与精力投入到研发、生产的本身。以创新测试工具加速相关领域技术发展,推动所服务行业的迭代更新,为人类文明进步增砖添瓦。

责任编辑:SemiInsights

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻