来源:内容由半导体行业观察(ID:icbank)

综合自

「

semiwiki

」,谢谢。

随着 DRAM 的不断发展和创新,它令人着迷。然而在过去的十年里,我经常读到 DRAM 由于难以缩放电容器而失去动力的观点。但事实上是自从 IBM 的 R. Dennard 博士发明DRAM以来,它仍在继续发展。1966 年,他引入了由一个晶体管和一个电容器组成的晶体管存储cell的概念。他的发明于 1968 年获得专利 (US3387286)。

多年来,DRAM采用一个晶体管存储cell的整体配置没有改变。55 年后的今天,我们拥有 3 家 1X 节点制造商,其存储容量超过 4 Gb,他们仍在制造具有相同配置的存储cell,包括一个晶体管和一个电容器。美光的 D1α,它是最先进的 DRAM,是第一个亚 15nm cell设计,

每个新的 DRAM 技术节点都生产出比其前一代更小、更紧凑的芯片。这种缩放允许每个晶片集成更多的芯片,这抵消了引入新技术所增加的制造成本。每一个新节点不仅会缩小cell尺寸,还会引入新材料或新架构布局。DRAM 技术已从沟槽电容器( trench capacitors )转向堆叠电容器(stacked capacitors)。电容器电介质已从单个high-K 层变为多个电介质层,电容器结构从冠状结构( crown structure)演变为柱状结构(pillar structure),布局现在从 10F2 修改为 8F2 到 6F2,其中 F 是最小特征尺寸。

我对cell布局特别感兴趣,并认为它是减少cell尺寸的重要参数。美光是第一家在 9x nm 节点上从 8F2 cell布局切换到 6F2 cell布局的公司,其次是三星在 80 nm 节点,最后是 SK-Hynix,它在 3x nm 节点的时候采用了 6F2 cell布局。我一直想知道什么时候会采用 4F2?在 4F2 cell中,字线间距和位线间距正好是 2F。4F2 配置需要环绕的垂直栅极结构。尽管在图案化和光刻方面取得了重大进展,但这个概念仍未实现,因为保持相同类型的架构并简单地进行修改而不是采用全新的设计更具成本效益。

在我还在一家以 IP 为中心的公司工作的时候,我能够快速检查 DRAM 4F2 专利的状态,并惊讶地发现三大内存制造商(三星、美光和 SK-海力士)在美国提交的有效专利总数) 不到几百,而且 2015 年之后的申请活动很少。这似乎表明该行业正专注于其他方面。

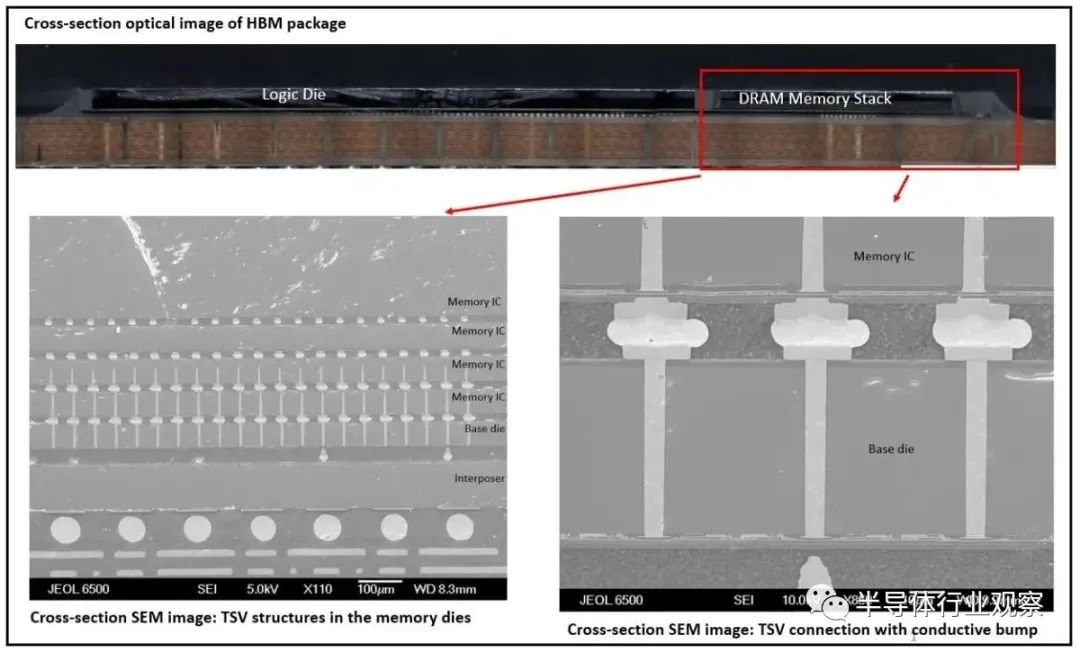

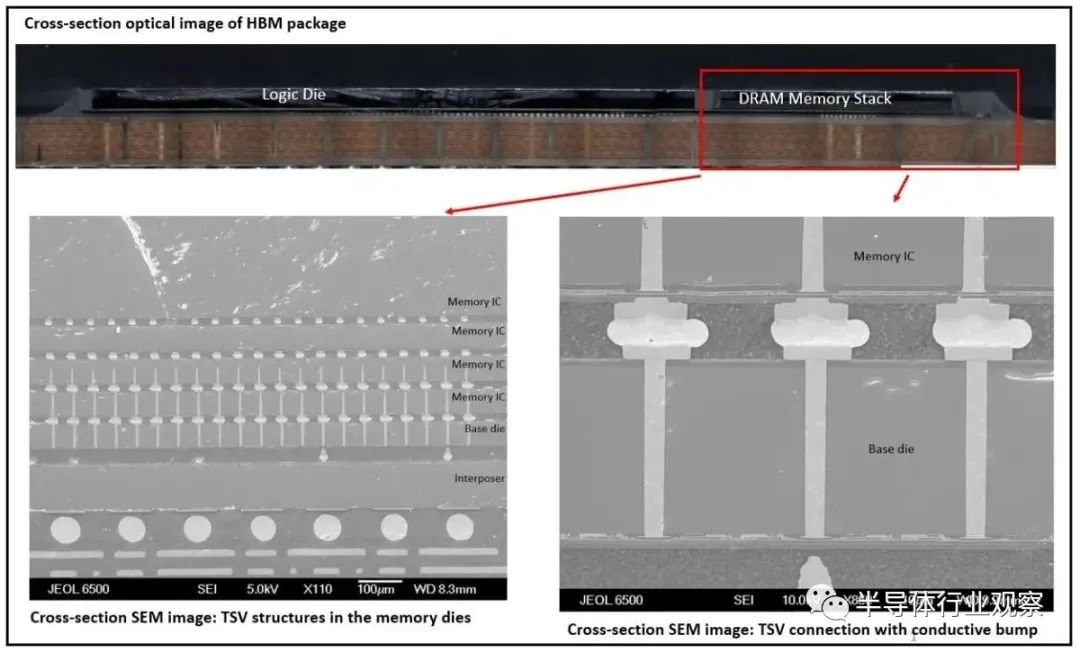

带宽是可以写入内存或可以从中读取的数据量,而延迟是对内存的请求与其执行之间的时间间隔。这个话题是当前内存行业的兴趣所在。2013 年,随着高带宽内存 (HBM) 的推出,带宽得到了最大的缓解,其中堆叠的 DRAM 芯片通过硅通孔 (TSV) 相互连接。图 1 显示了 HBM 的分析。HBM 及其 TSV 结构改进了逻辑过程和内存之间的数据传输,但它并没有完全解决“内存墙”问题。

我经常想知道下一步会是什么,然后我看到了 2021 年电子元件和技术会议 (ECTC) 的会议记录,这是与封装、元件和微电子系统相关的主要国际活动之一。

本次会议有来自 GlobalFoundries、IBM、英特尔、美光三星和台积电等主要设备制造商的论文。所有这些公司都讨论了混合键合、直接键合、die到die连接以及各种无 TSV 解决方案。引起我注意的一篇论文由 Micron Memory Japan 和其他几个研究组织共同撰写的,标题为“Ultra-thinning of 20 nm Node DRAMS down to 3 µm for Wafer-on-Wafer (WOW) applications”的文章。在此文中,他们描述了如何使用研磨和化学机械抛光 (CMP) 两种不同的方法来减薄晶圆,并比较减薄前后 DRAM 的保留时间。基于此,他们得出的结论是——保留性能并未因减薄过程而恶化。

这确实是一篇令人眼前一亮的论文。因为自从引入 HBM 以来,晶圆厚度已经从几百微米锐减到 40 µm 左右,但达到 3 µm 是非常了不起的。相比之下,人的头发约为 70 µm ±20 µm。混合键合和晶圆减薄的结合为 DRAM 开辟了新的可能性。在混合键合中,两个晶圆的金属键合焊盘以及与它们相邻的介电材料也被直接连接。混合键合已在业界使用,并已被索尼用于其图像传感器中,但是,截至今天,它还尚未在堆叠式 DRAM 产品中实施。混合键合的挑战之一是它需要原子平面级别的干净界面。

薄晶圆的生产和混合键合将大大降低 TSV 阻抗,它还会增加数据带宽,降低热阻,最终增加互连密度。如果使用这种技术,那么图 1 上的图像将不会在芯片之间看到导电凸块,并且存储器芯片的厚度将薄十倍,这将导致堆叠高度的整体降低。

与最近在科学界讨论的单片 3D DRAM 等全新配置相比,超薄晶圆与混合键合的这种组合将更容易延长 DRAM 设备的寿命。可以设想新的应用,例如使用直接绑定到逻辑芯片上的 DRAM 堆栈,或者它可以用作缓存存储器,像 AMD 和其他一些公司正在实施他们的外部 SRAM 存储器。当然,对于 DRAM 设备,某些架构设计需要修改,因为截至今天,SRAM 在延迟方面优于 DRAM。在逻辑芯片上安装薄型 DRAM 芯片还可以带来新概念,例如内存中的计算,其中 HBM 中的基础芯片可以具有一定的计算能力。

DRAM 远未走到生命尽头,还有很长的路要走。它需要进一步缩小以降低成本。可能在未来,外围电路也将按比例缩小甚至从DRAM芯片中取出,制成独立芯片,然后使用超薄工艺和混合键合技术安装在DRAM上。先进光刻和图案化的结合、将外围电路分解为单个小芯片(或“小芯片”)配置的可能性、晶圆减薄工艺和混合键合技术的可用性使 DRAM 设备重新焕发活力。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2810内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!