芯驰E3650:为理想星环OS保驾护航(一)

2025-11-26

15:59:35

来源: 芯驰科技

点击

01. 引言

4.4 片上非易失性存储 eNVM

4.5 IRAM_LP:低功耗域的"守夜人"

• 高级特性

• 智能预取机制支持数据预取,多个专用主组(Master Group)和1个共享组,大幅提升连续访问性能

• 内联AES128加密支持内联AES128保护,在数据传输过程中实时加解密,确保存储数据安全

• 加密密钥管理内置加密密钥管理功能,支持多个密钥存储和管理,满足功能安全要求

• 主从通信模式支持主从通信模式,可实现XSPI控制器之间的互联

这些设计确保了在最坏情况下,内存访问延迟依然可控,满足硬实时分析的要求。

当智能汽车以120km/h的速度疾驰时,每一毫秒的计算延迟都可能关乎生命安全。在理想汽车星环OS(HaloOS)的硬实时系统中,MCU芯片承担着整个系统的"神经中枢"角色——它必须在严格的时间约束内,精准完成从传感器数据采集、实时决策到执行器控制的全链路处理。作为HaloOS 的智控首发平台和核心MCU供应商,芯驰科技的E3650芯片正是为这样的极致要求而生。今天,我们将揭秘E3650如何通过创新的性能与架构设计,为智能汽车的硬实时系统提供坚实的算力基础。

02. 为什么智能汽车需要高性能MCU?

在传统汽车电子系统中,MCU主要处理相对简单的控制任务。但在智能汽车时代,系统复杂度呈指数级增长:

• 多传感器融合:需要同时处理来自雷达、摄像头、超声波等多路传感器的实时数据。

• 复杂算法执行:从简单的PID控制升级到复杂的融合算法、决策逻辑和预测模型。

• 严苛的实时性:要求在硬实时系统中,任何一个环节的延迟都可能导致系统失效。

• 复杂算法执行:从简单的PID控制升级到复杂的融合算法、决策逻辑和预测模型。

• 严苛的实时性:要求在硬实时系统中,任何一个环节的延迟都可能导致系统失效。

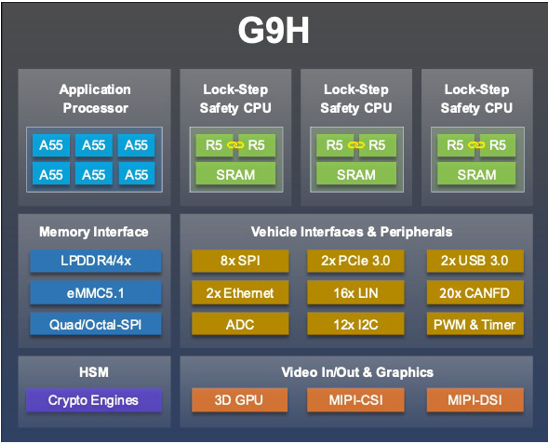

03. E3650的多核异构架构:为实时而生

3.1 架构总览

E3650采用业界领先的多核异构架构,针对不同的实时需求进行了精心设计:

• 高性能Cortex-R52+主核

• 高算力强实时R52+集群,行业同等级最高主频600MHz

• 支持锁步模式(Lockstep),满足ASIL-D功能安全要求

• 专为实时控制优化,中断响应延迟低至纳秒级

• 多功能Cortex-R5辅助核心

• 超强算力信息安全CPU,吞吐率倍数于竞品的硬件加速器,硬件支持国密算法

• 低功耗CPU,极致的运行/静态功耗,支持丰富的唤醒源

• 硬件加速单元

• SSDPE硬件通信引擎,CAN/CANFD转发不占用CPU

• 双路GBit以太网(TSN),支持硬件环网架构,可节省Switch芯片

• 高算力强实时R52+集群,行业同等级最高主频600MHz

• 支持锁步模式(Lockstep),满足ASIL-D功能安全要求

• 专为实时控制优化,中断响应延迟低至纳秒级

• 多功能Cortex-R5辅助核心

• 超强算力信息安全CPU,吞吐率倍数于竞品的硬件加速器,硬件支持国密算法

• 低功耗CPU,极致的运行/静态功耗,支持丰富的唤醒源

• 硬件加速单元

• SSDPE硬件通信引擎,CAN/CANFD转发不占用CPU

• 双路GBit以太网(TSN),支持硬件环网架构,可节省Switch芯片

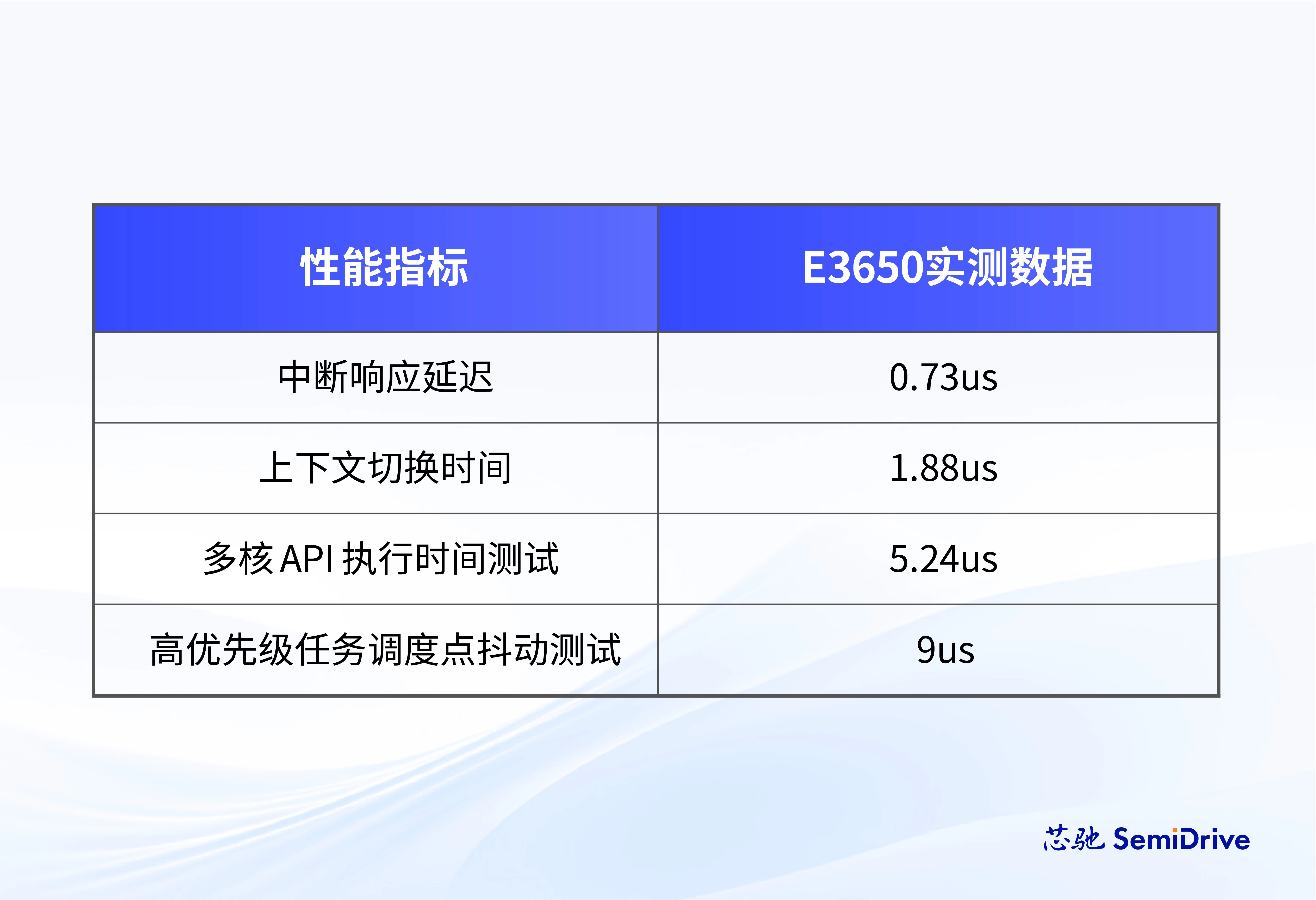

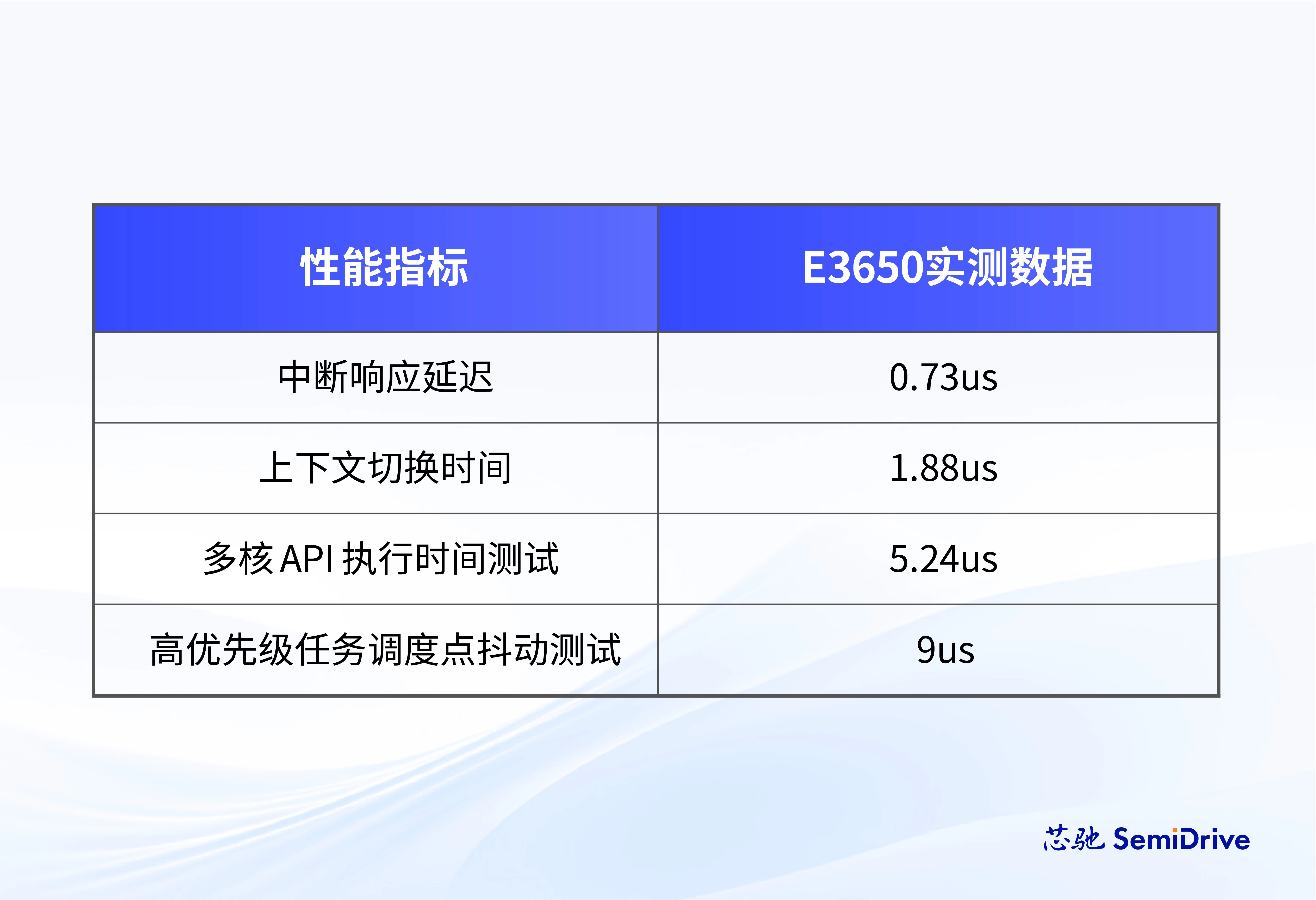

3.2 实时性能指标

基于E3650的架构特性,在HaloOS的实际应用中,我们测得以下关键性能指标:

04. 内存架构:消除性能瓶颈

再强的 CPU,如果没有高效的内存系统支撑,也会成为"巧妇难为无米之炊"。E3650在内存架构上做了精心设计。

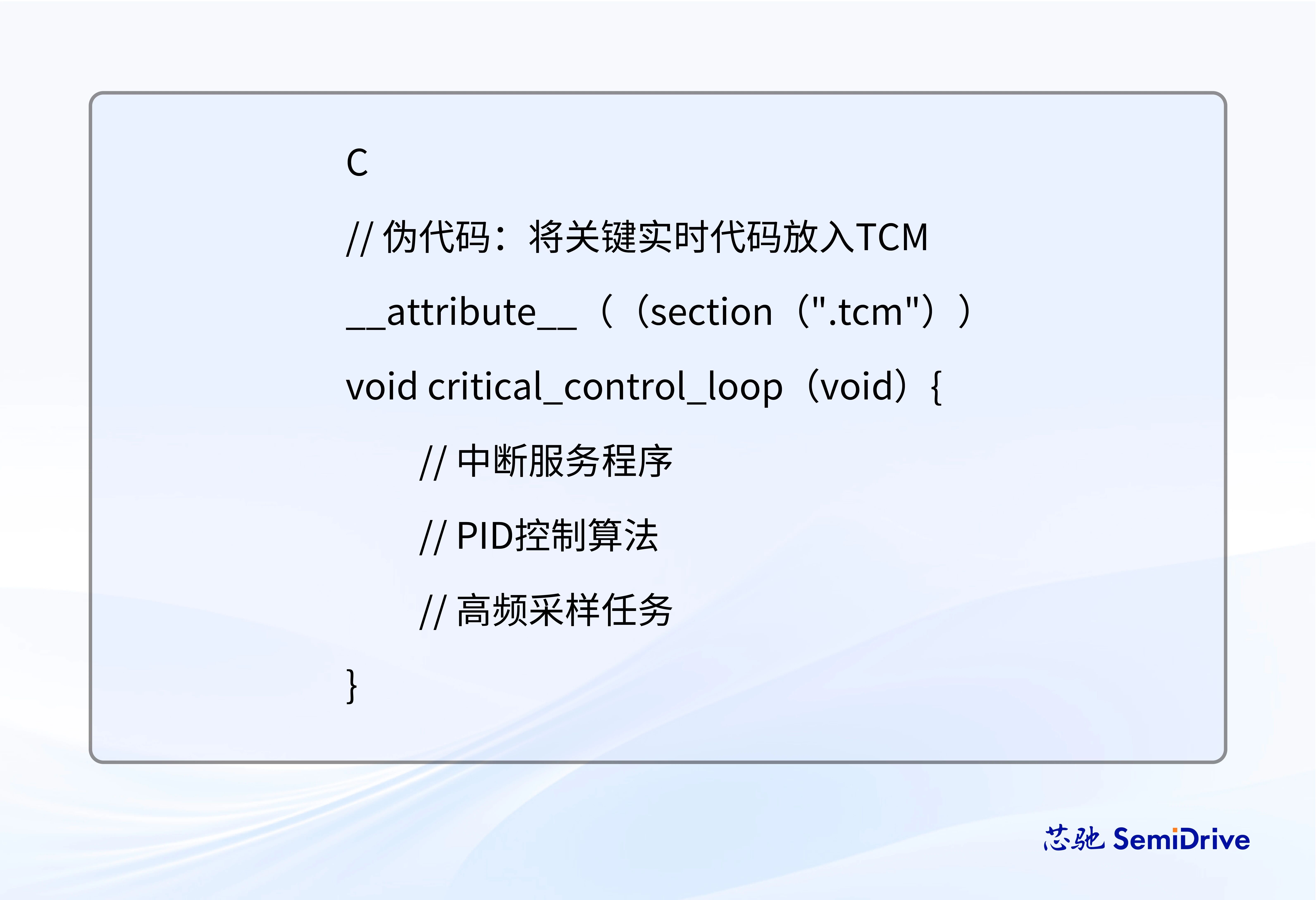

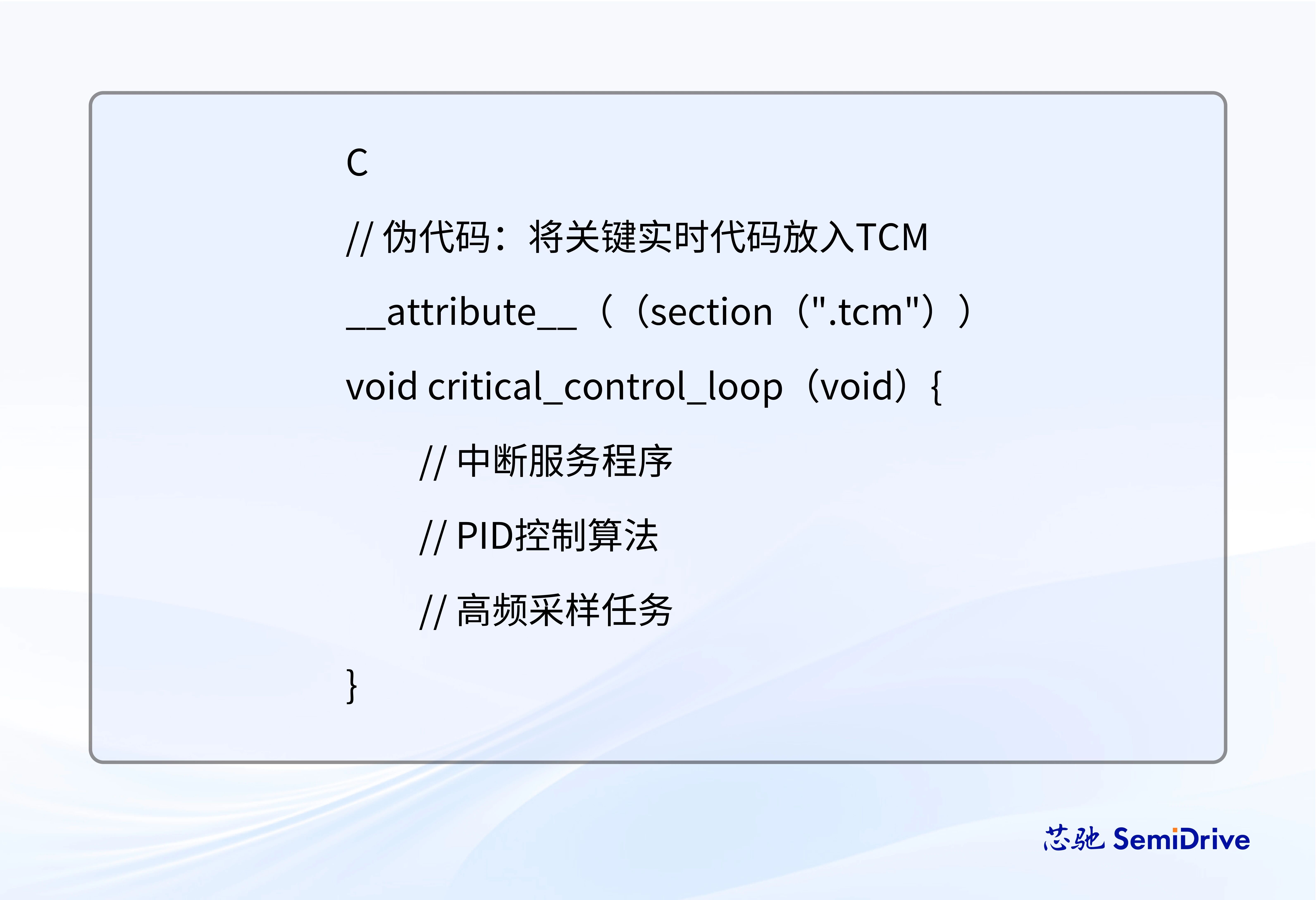

4.1 TCM(紧耦合内存)

紧耦合内存(TCM,Tightly Coupled Memory)是E3650实时性能的第一道保障。

• 核心特性

• 每核独享128KB:避免总线竞争,访问延迟为零等待周期(2个多功能核各自具有 64KB TCM);

• 直连CPU核心:物理位置紧邻处理器,数据路径最短;

• 无缓存干扰:不经过Cache,访问时间100%确定;

• 每核独享128KB:避免总线竞争,访问延迟为零等待周期(2个多功能核各自具有 64KB TCM);

• 直连CPU核心:物理位置紧邻处理器,数据路径最短;

• 无缓存干扰:不经过Cache,访问时间100%确定;

• 典型应用场景

在HaloOS中,可将所有ASIL-D级别的控制代码和中断向量表都部署在TCM中,确保最坏情况执行时间(WCET)的绝对可预测性。

在HaloOS中,可将所有ASIL-D级别的控制代码和中断向量表都部署在TCM中,确保最坏情况执行时间(WCET)的绝对可预测性。

4.2 IRAM:片上"高速公路网"

片上SRAM (IRAM)是E3650的第二层内存体系,提供了大容量的的高速存储空间。E3650的IRAM控制器支持ECC功能,可工作在两种模式:

• 模式一:ECC使能(安全优先):

• 数据 RAM + ECC RAM:采用(64,8)汉明码;

• 单比特纠错+双比特检测(SECDED);

• 每 64 位数据 RAM 配备 8 位 ECC RAM,总计提供额外的 1/8 空间用于ECC;

• 适用场景:功能安全要求高的关键数据存储;

• 模式二:ECC禁用(容量优先)

• 纯数据存储:ECC RAM空间可转为数据RAM使用,提供额外的存储空间;

• 适用场景:对容量需求大、安全等级要求相对较低的应用;

• 数据 RAM + ECC RAM:采用(64,8)汉明码;

• 单比特纠错+双比特检测(SECDED);

• 每 64 位数据 RAM 配备 8 位 ECC RAM,总计提供额外的 1/8 空间用于ECC;

• 适用场景:功能安全要求高的关键数据存储;

• 模式二:ECC禁用(容量优先)

• 纯数据存储:ECC RAM空间可转为数据RAM使用,提供额外的存储空间;

• 适用场景:对容量需求大、安全等级要求相对较低的应用;

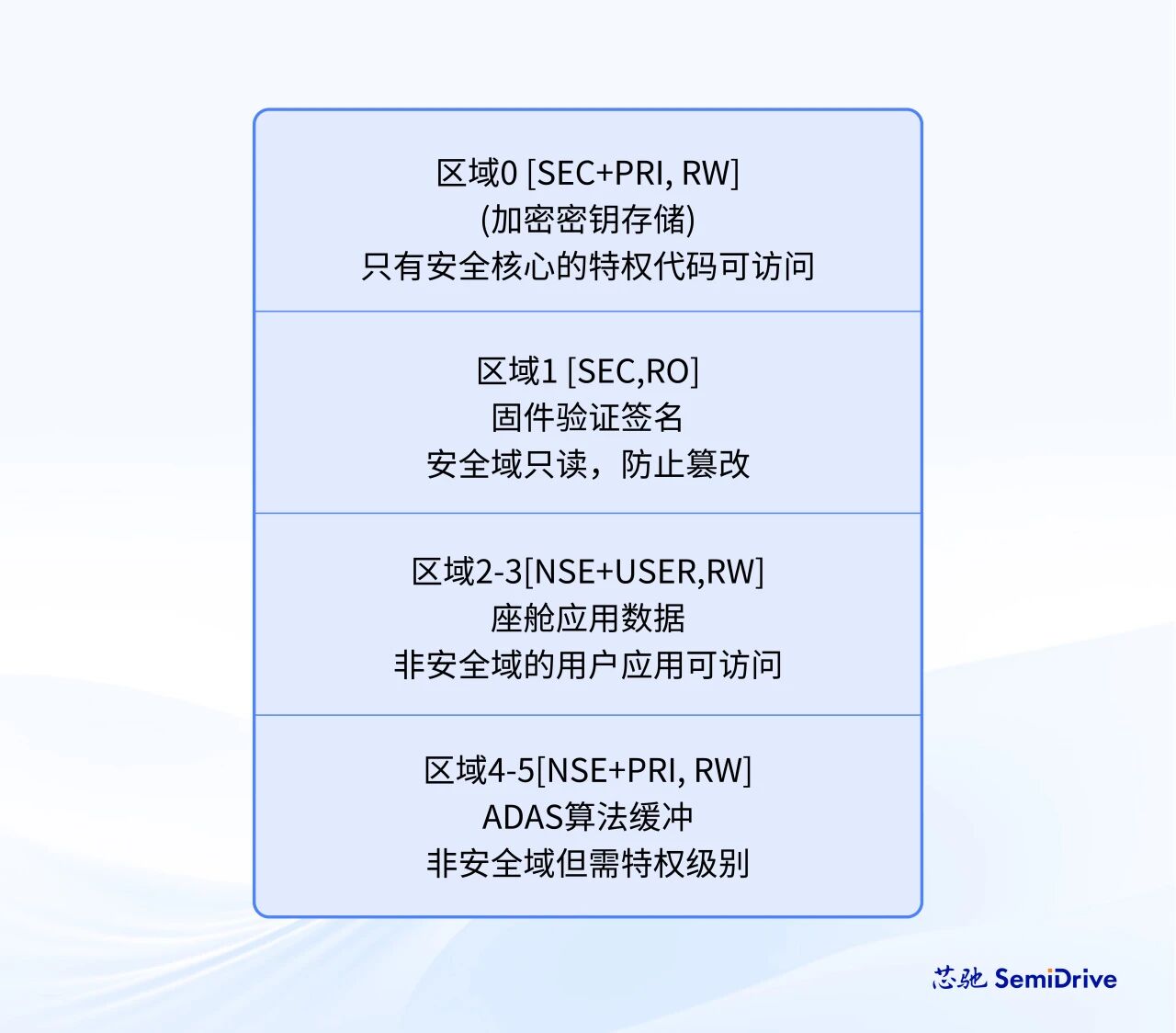

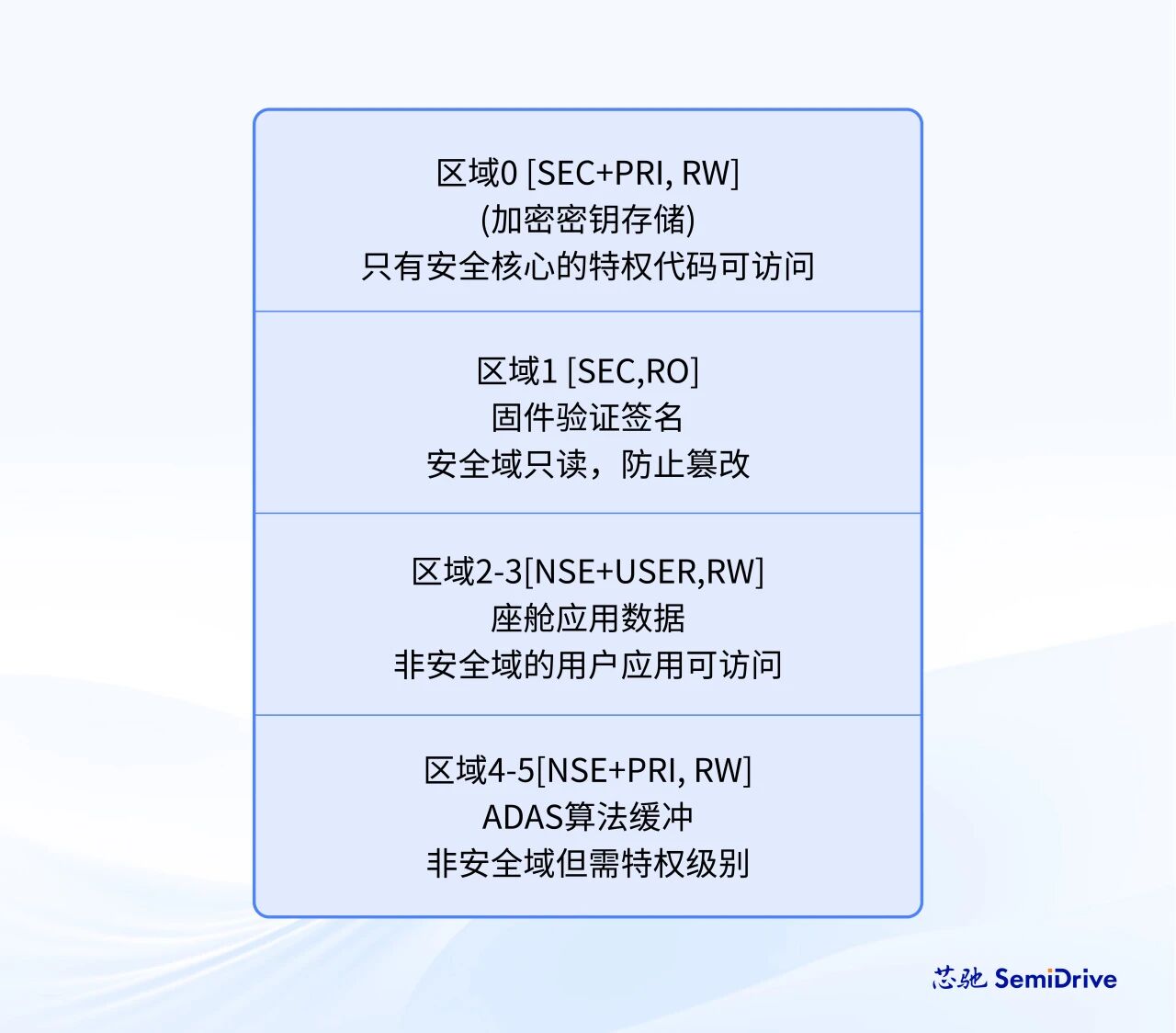

4.3 CRAM:权限管理的"智能网关"

在汽车芯片领域,谈到片上存储,大家最熟悉的莫过于上述的 IRAM(Internal RAM)。但芯驰E3650采用的CRAM(Coherency RAM)却远不止是一块简单的内存,它更像是一位智能管家,不仅提供存储空间,还负责数据安全、访问控制和错误防护。

传统MCU的IRAM就像一个"公共仓库":任何有权限的模块都能随意读写,没有区域划分,也缺乏数据保护机制。这在功能安全要求日益严苛的汽车电子领域,已经难以满足需求。

芯驰E3650的CRAM则完全不同。它在保留高性能直接访问特性的同时,引入了安全管控能力,让片上存储真正成为系统安全架构的一部分。

传统MCU的IRAM就像一个"公共仓库":任何有权限的模块都能随意读写,没有区域划分,也缺乏数据保护机制。这在功能安全要求日益严苛的汽车电子领域,已经难以满足需求。

芯驰E3650的CRAM则完全不同。它在保留高性能直接访问特性的同时,引入了安全管控能力,让片上存储真正成为系统安全架构的一部分。

优势一:分区管理

CRAM 支持将内存划分为8个独立区域,每个区域都有独立的起止地址和访问权限配置。这就像把一个大仓库改造成了带门禁的分区储藏室,在一颗运行AUTOSAR的汽车ECU中,您可以这样规划:

• 区域0-1:存放安全域的关键算法和密钥,仅允许安全核心读写

• 区域2-3:存放应用层的实时数据缓冲,允许应用核心访问

• 区域4-5:诊断数据区,允许诊断服务读取但禁止写入

• 区域6-7:预留给OTA升级临时数据

• 区域2-3:存放应用层的实时数据缓冲,允许应用核心访问

• 区域4-5:诊断数据区,允许诊断服务读取但禁止写入

• 区域6-7:预留给OTA升级临时数据

优势二:多维权限控制

CRAM引入了4级权限体系:

• 安全域(SEC) vs 非安全域(NSE)

• 特权模式(PRI) vs 用户模式(USER)

• 安全域(SEC) vs 非安全域(NSE)

• 特权模式(PRI) vs 用户模式(USER)

每个区域的访问权限可以独立配置为:禁止访问、只写、只读、读写四种模式。CRAM区域规划示例如下,这种设计确保了即使座舱系统的某个第三方App存在漏洞,也无法窃取ADAS系统的传感器数据或篡改安全核心的密钥。

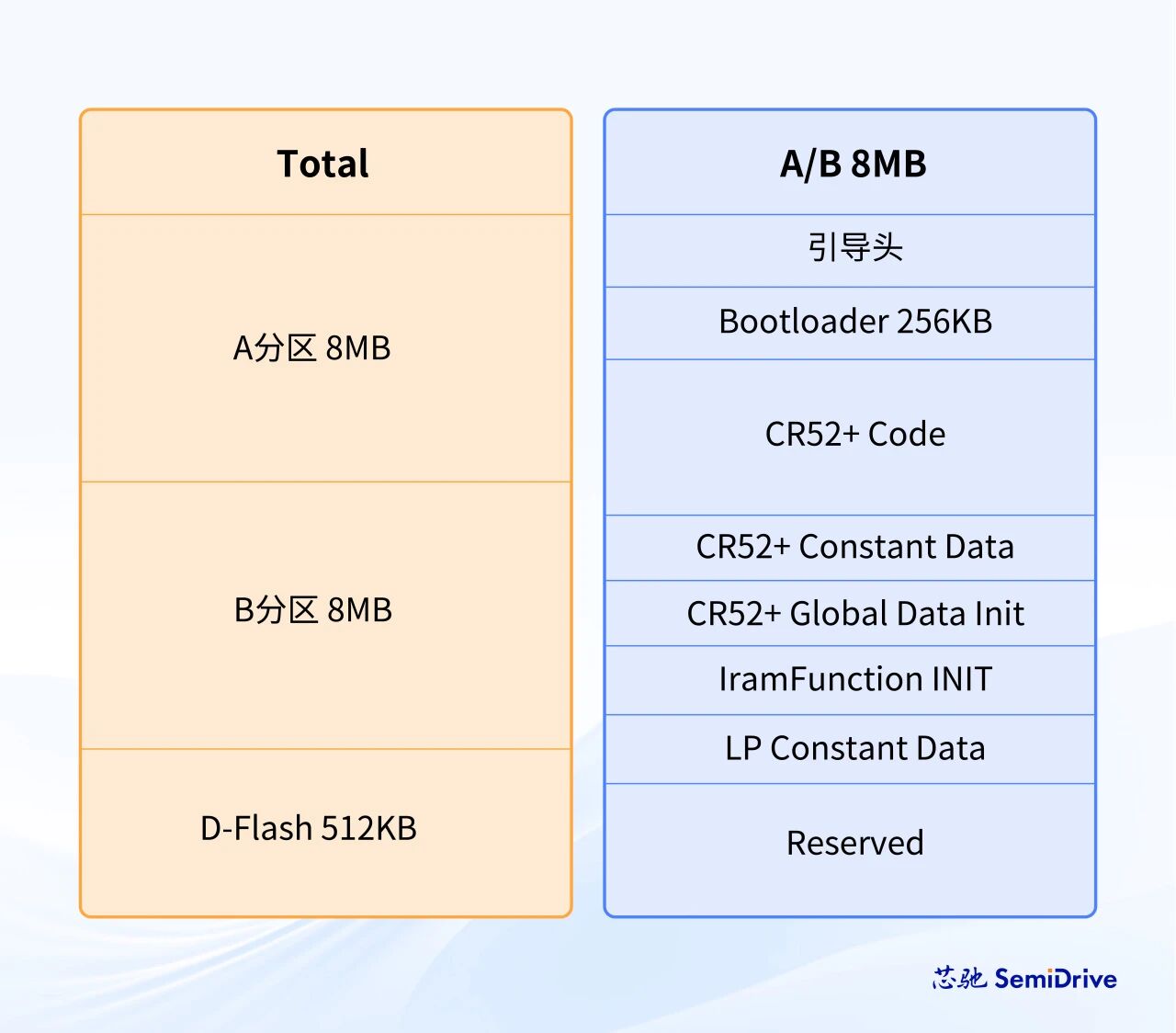

4.4 片上非易失性存储 eNVM

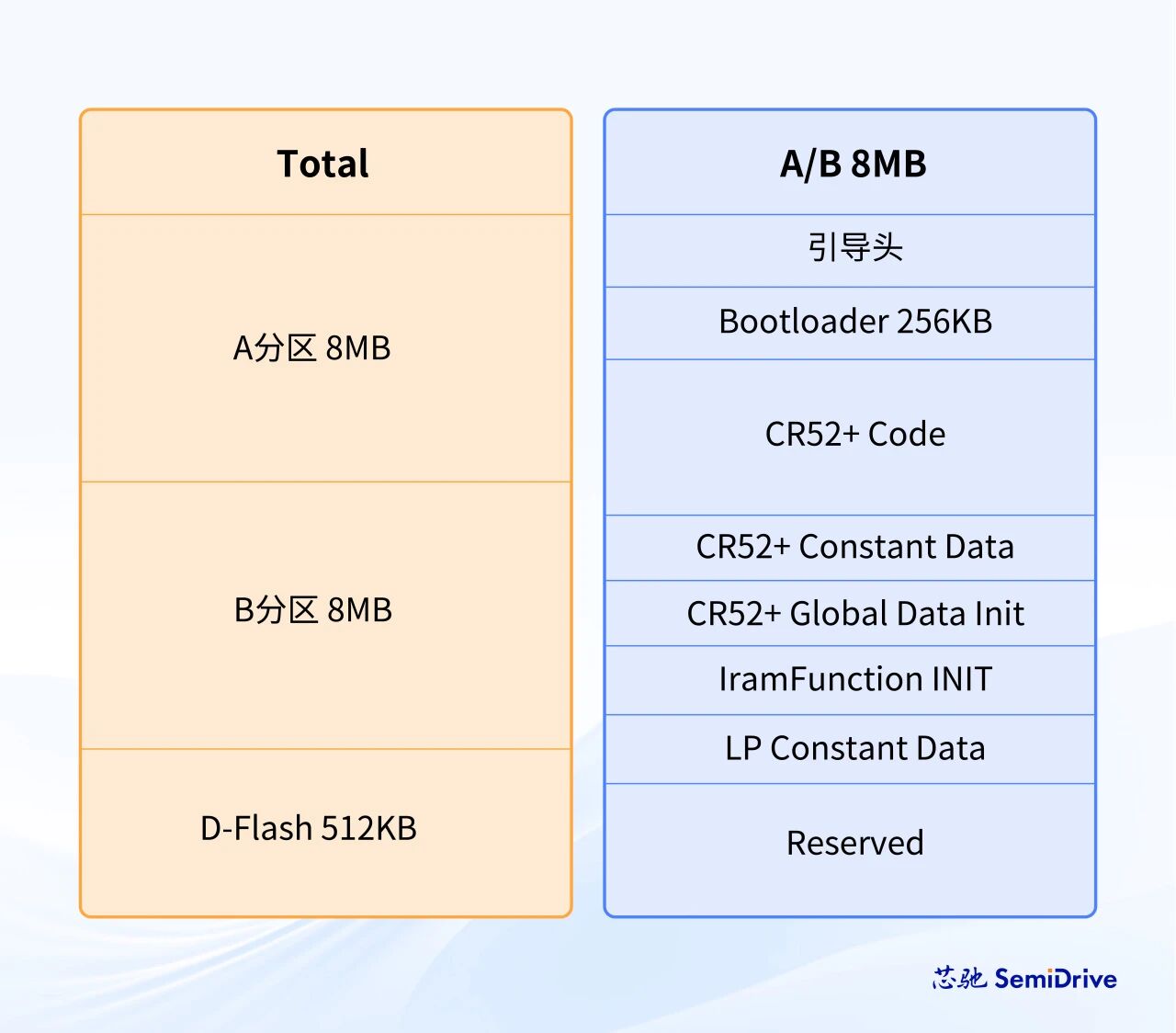

芯驰E3650集成专为车规级应用设计的高性能非易失性存储解决方案,提供了16.5MB的非易失存储能力。支持双区架构及 A/B 分区启动、安全启动等关键特性,HaloOS可轻松应用E3650实现安全的OTA升级。

• ECC错误保护:

• 支持ECC检错机制和记录错误地址;

• 对于可纠正的ECC错误,硬件自动重试读取直到数据正确或达到最大重试次数;

• 重试次数可配置,并提供重试成功计数器;

• HSM安全镜像区域:

• 专为硬件安全模块(HSM)预留高安全镜像区域;

• 支持HSM密钥区域保护,仅允许HSM读取或HSM核心在特定信号下写入;

• 支持ECC检错机制和记录错误地址;

• 对于可纠正的ECC错误,硬件自动重试读取直到数据正确或达到最大重试次数;

• 重试次数可配置,并提供重试成功计数器;

• HSM安全镜像区域:

• 专为硬件安全模块(HSM)预留高安全镜像区域;

• 支持HSM密钥区域保护,仅允许HSM读取或HSM核心在特定信号下写入;

4.5 IRAM_LP:低功耗域的"守夜人"

相比通用的 IRAM,IRAM_LP 不仅在低功耗模式下可用,更可提供灵活的容量禁用机制,可实现分级功耗控制,支持用户实现分场景功耗策略,运行模式全开,待机模式部分禁用,深度睡眠大幅禁用。

• 000: 128KB全开启(高性能模式)

• 001: 禁用16KB,保留112KB(性能优先)

• 010: 禁用32KB,保留96KB

• 011: 禁用48KB,保留80KB

• 100: 禁用64KB,保留64KB(平衡模式)

• 101: 禁用80KB,保留48KB

• 110: 禁用96KB,保留32KB

• 111: 禁用112KB,仅保留16KB(极致省电)

• 001: 禁用16KB,保留112KB(性能优先)

• 010: 禁用32KB,保留96KB

• 011: 禁用48KB,保留80KB

• 100: 禁用64KB,保留64KB(平衡模式)

• 101: 禁用80KB,保留48KB

• 110: 禁用96KB,保留32KB

• 111: 禁用112KB,仅保留16KB(极致省电)

4.6 外部XSPI接口(扩展串行外设接口)

E3650集成了业界领先的XSPI(扩展串行外设接口)控制器,为系统提供灵活高效的外部存储扩展能力。XSPI是Hyperbus接口的超集,支持Hyperflash和HyperRAM设备访问,同时兼容标准的SPI Flash设备。

• 核心特性:

• 多通道架构支持双通道1/4/8位数据线SPI flash和HyperRAM,每通道支持2个片选引脚,可同时连接多个存储设备

• 高带宽支持支持8位数据线flash和HyperRAM,提供更高的数据吞吐率•灵活的数据率支持SDR(单倍数据率)和DDR(双倍数据率)模式,适应不同性能需求

• XIP模式支持XIP(就地执行)模式,CPU可直接从外部Flash执行代码,无需先加载到RAM

• 多通道架构支持双通道1/4/8位数据线SPI flash和HyperRAM,每通道支持2个片选引脚,可同时连接多个存储设备

• 高带宽支持支持8位数据线flash和HyperRAM,提供更高的数据吞吐率•灵活的数据率支持SDR(单倍数据率)和DDR(双倍数据率)模式,适应不同性能需求

• XIP模式支持XIP(就地执行)模式,CPU可直接从外部Flash执行代码,无需先加载到RAM

• 高级特性

• 智能预取机制支持数据预取,多个专用主组(Master Group)和1个共享组,大幅提升连续访问性能

• 内联AES128加密支持内联AES128保护,在数据传输过程中实时加解密,确保存储数据安全

• 加密密钥管理内置加密密钥管理功能,支持多个密钥存储和管理,满足功能安全要求

• 主从通信模式支持主从通信模式,可实现XSPI控制器之间的互联

• 典型应用场景

• 外设扩展可搭配芯驰 E3010 扩展芯片,灵活拓展 SPI、PWM捕获、PWM输出、ADC等多种数字、模拟接口

• 启动代码存储将启动代码存储在外部Flash,支持XIP直接执行,节省宝贵的片上存储资源

• 固件更新存储存储备用固件和配置数据,支持安全的在线升级

• 日志记录存储利用大容量外部存储记录系统运行日志和诊断数据

• 外设扩展可搭配芯驰 E3010 扩展芯片,灵活拓展 SPI、PWM捕获、PWM输出、ADC等多种数字、模拟接口

• 启动代码存储将启动代码存储在外部Flash,支持XIP直接执行,节省宝贵的片上存储资源

• 固件更新存储存储备用固件和配置数据,支持安全的在线升级

• 日志记录存储利用大容量外部存储记录系统运行日志和诊断数据

通过智能预取和缓存管理,XSPI接口可以有效降低外部存储访问延迟,提升系统整体性能。在DDR模式下,配合8位数据宽度,可以达到极高的数据传输速率,满足实时系统对外部存储的苛刻要求。

4.7 确定性内存访问

在硬实时系统中,内存访问的确定性比平均性能更重要。E3650通过以上硬件机制保证:

• 独占访问路径TCM可设置为每核独占,避免总线竞争;

• 优先级仲裁内存总线支持优先级,高优先级任务优先访问;

• 缓存锁定关键代码可锁定在缓存中,避免不确定的缓存miss;

• 优先级仲裁内存总线支持优先级,高优先级任务优先访问;

• 缓存锁定关键代码可锁定在缓存中,避免不确定的缓存miss;

这些设计确保了在最坏情况下,内存访问延迟依然可控,满足硬实时分析的要求。

05. 总结与预告

E3650的高性能多核架构为HaloOS的硬实时系统提供了坚实的算力基础:

• 多核高算力:强大且确定的实时计算能力

• 硬件调度支持:极低开销的任务切换和优先级管理

• 多层次内存:消除内存瓶颈,确保访问确定性

• 硬件调度支持:极低开销的任务切换和优先级管理

• 多层次内存:消除内存瓶颈,确保访问确定性

性能只是芯片的一个维度。在下一期文章中,我们将深入探讨E3650如何通过功能安全设计和冗余机制,确保即使在极端故障情况下,系统依然能够安全可控。

在汽车电子领域,安全永远是第一位的。敬请期待!

在汽车电子领域,安全永远是第一位的。敬请期待!

【关于芯驰】

芯驰科技是全场景智能车芯引领者,专注于提供高性能、高可靠的车规芯片,覆盖智能座舱和智能车控领域,涵盖了未来汽车电子电气架构最核心的芯片类别。

芯驰科技是全场景智能车芯引领者,专注于提供高性能、高可靠的车规芯片,覆盖智能座舱和智能车控领域,涵盖了未来汽车电子电气架构最核心的芯片类别。

芯驰拥有超200个定点项目,服务260余家客户,覆盖国内90%以上主机厂及多家国际主流车企,包括上汽、奇瑞、长安、东风、一汽、日产、本田、大众、理想等。目前,芯驰全系列芯片均已量产,累计出货量突破900万片,搭载于130余款主流车型。五大认证 放芯驰骋·德国莱茵TÜV ISO 26262 ASIL D功能安全管理体系认证·AEC-Q100 Grade 1/Grade 2可靠性认证·德国莱茵TÜV ISO 26262 ASIL B/D 功能安全产品认证·德国莱茵TÜV ISO/SAE 21434汽车网络安全管理体系认证·工商总局、国家密码管理局国密信息安全双认证。

责任编辑:SemiInsights

-

- 半导体行业观察

-

- 摩尔芯闻