芯片复杂度提升,测试架构如何进化?

2026-03-09

11:55:00

来源: 互联网

点击

背景

随着半导体制程技术向 2nm 节点逼近,单纯依赖电子互连已难以平衡超大规模算力集群与严苛功耗控制之间的矛盾。在 2025 年至 2026 年的行业周期内,人工智能(AI)大模型的训练需求正驱动数据中心向百万级 GPU 规模的“AI 工厂”演进,这使得机架间(Inter-rack)及芯片间的高速通信面临严重的带宽与散热瓶颈。

为了突破电互连的物理极限,共封装光学(CPO, Co-packaged Optics) 已成为半导体行业公认的战略级演进方向。特别是在英伟达(NVIDIA)宣布在其下一代高速互连架构中深度引入 CPO 技术后[1],该领域已从实验室研究迅速转化为产业共识。CPO 通过将光引擎与计算 ASIC 共同封装,显著缩短了电信号传输路径,实现了跨越式的性能提升:其能量消耗仅为传统可插拔光模块的 1/3.5,并显著提升信号完整性与系统可靠性。通过这种深度集成,在降低电损耗的同时使 GPU 集群的计算利用率提升了 20% 以上。

然而,这种高度集成的光电融合架构也为测试带来了“黑盒挑战”。传统的以硬件为中心(Hardware-centric)、单一功能的测试设备由于布线冗余和数据流孤岛,已无法适应这种需要实时反馈、高集成度的验证环境。这种从物理链路瓶颈到测量复杂度剧增的转变,迫切需要一种能够随应用场景灵活演进的数字化可重构测试架构。

可重构测试测量解决方案

面对 CPO 和异质集成带来的复杂度压力,Liquid Instruments 开发的 Moku 平台通过“可重构硬件+软件定义仪器”架构实现了测试范式的飞跃。该平台利用高性能 FPGA 的实时处理能力,将示波器、锁相放大器、频谱分析仪及 PID 控制器等 16 种以上精密仪器整合于单一硬件内核中,极大地压缩了测试系统的物理足迹。

FPGA 的部分重构能力使得用户能够构建低延迟、定制的测试配置,简化布线并减少信号损耗。相比传统固定功能仪器,可重构平台兼具高性能、灵活性与实时闭环能力,支持快速搭建与动态重构,并通过多仪器、多通道并行测试降低成本,提升自动化水平与测试效率。同时,其可升级、可扩展特性使系统能随需求迭代灵活调整测试测量方案。这种架构的核心优势在于其数字化互连能力,Moku:Delta利用内部高达 160 Gb/s 的数字总线,使信号在不同仪器槽位间流转时无需经过外部物理电缆,从而彻底消除了由外部线缆引入的相位偏移,噪声与寄生效应。此外,其专利的混合 ADC 采样技术通过数字化混合高采样率与高分辨率通道,为表征半导体器件中的 1/f 闪烁噪声及微弱光电信号提供了极其纯净的信号底噪。

当这种平台化的灵活性被引入具体的研发流程时,复杂的系统调优便从繁琐的硬件堆叠转变为敏捷的算法迭代,这在英特尔实验室(Intel Labs)的硅光研究中得到了印证。

设计开发:硅光芯片集成控制维度上升后,自动化闭环调控不可或缺

当控制维度持续增加时,测试系统本身必须具备动态重构与自动化闭环能力,才能匹配器件复杂度的增长。

在英特尔实验室进行的硅基光电异质集成技术研究中,为片上多个相位调制器(Phase Tuner)寻找最优偏置条件,是实现最佳系统表现的关键步骤。相位调制器的性能直接决定了光系统的干涉特性,但由于半导体制造过程中的工艺波动(Manufacturing Variations),每个调制器的半波电压(V_{\pi})偏置点都存在细微差异。寻找最优偏置点不仅是为了参考校准,更是为了在开启和关闭状态之间维持良好的消光比(Extinction Ratio),并确保调制精度以最小化调制误差。

这类寻优任务通常需要通过多维扫描与复杂的测试流程来完成。然而,随着系统参数调节维度的增加,传统脚本的复杂程度与计算时间呈指数级增长,严重影响验证效率。传统解决方案一般依赖于由多个“单一固定功能”的台式仪器(如锁相放大器、PID 控制器等)堆叠组合,由于被测样品集成度高,传统方案布线复杂、占用空间巨大,且缺少直观的显示界面,不利于团队协作与快速上手。

在英特尔实验室看来,这类任务里真正决定效率的不再是单个仪器的标称精度,而是系统层面的三个关键能力:

信号并行处理能力:支持同时运行多个关键测试环节,以缩短扫描迭代时间;

信号全阶段可视化:直观的路径显示让调参与验证过程清晰可见,降低学习成本;

系统配置可复用:将复杂的测量配置简化为可一键加载的操作,降低团队复现成本。

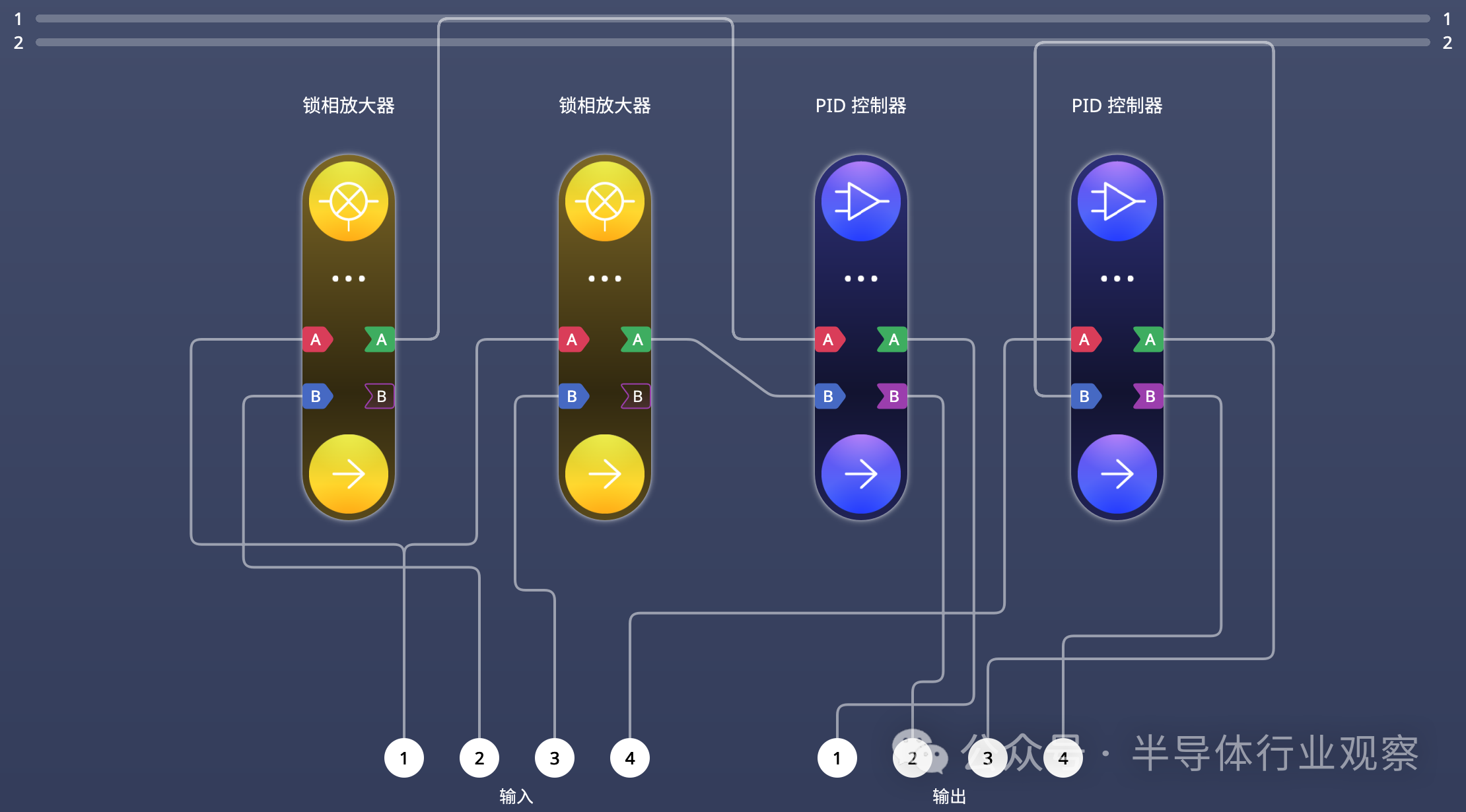

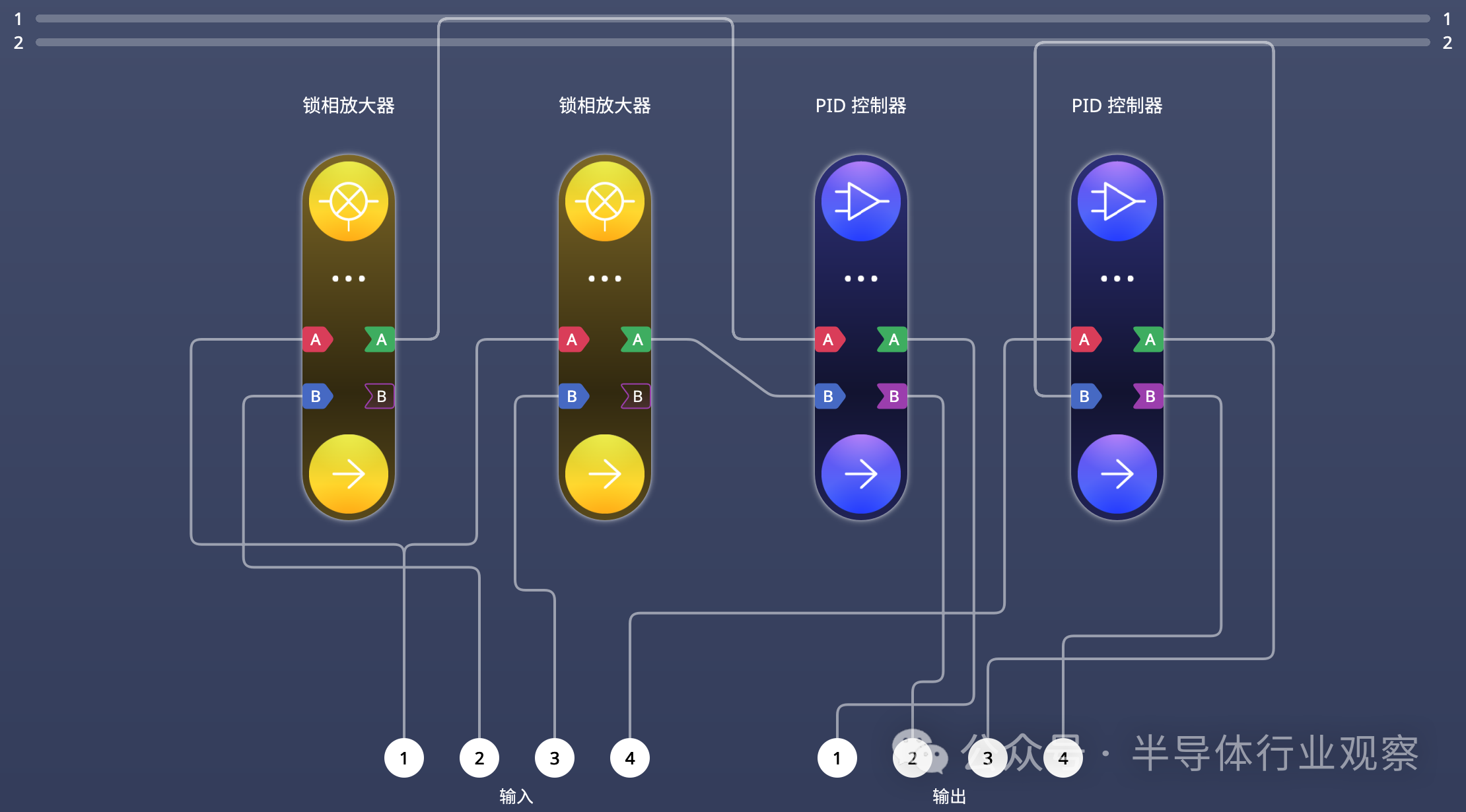

研究团队最终转向了基于 FPGA 的 Moku 高性能测试测量平台。通过多仪器并行模式 (Multi-Instrument Mode),团队在一个硬件平台上同时运行了两个锁相放大器与两个 PID 控制器[2]。高精度 ADC 确保了被测信号的还原度和高分辨率,在显著减少系统占地的同时,依赖内部无损数字互连消除了物理布线带来的干扰。

实施效果:借助图形化显示界面,团队得以直观地捕获信号的传递特性。英特尔实验室的光电研究科学家 Guan-lin Su 博士指出:“在使用多维扫描时,通常需要数百个步骤来进行收敛,而 Moku 帮助我们在几次迭代中就能完成这项工作。” Moku 的单一设备集成方案不仅使实验设置变得更快、更高效,其保存/加载配置的功能也极大地提升了团队间的协作效率。

图 1:Moku多仪器并行模式配置:同时运行多个锁相放大器和PID控制器

量产制造:复杂背景下,解决方案满足多样化和特定化的测试需求

真正的效率提升来自“方案可变性”,而非某一种固定技术。

Intel 的案例证明了 Moku 在系统研发中的闭环调控通量,而 AMD 的实践则进一步揭示了它在失效分析及量产检测这一极限信号环境下的微弱信号探测及恢复能力。

在失效分析(Failure Analysis)与量产制造阶段,AMD 展示了如何利用 Moku 平台的灵活性解决激光探测技术中的复杂瓶颈[3]。以晶圆缺陷检测为例,最大的挑战在于如何在复杂背景噪声下提取极其微弱的故障信号,这要求测试系统同时兼顾扫描效率与信噪比,并能快速切换不同的测试方案。

传统的激光探测方案受制于设备商之间的技术壁垒,缺乏定制能力。AMD 团队采用了可重构 FPGA 平台 Moku,将其既作为测试仪器,也作为可编程的信号处理架构:

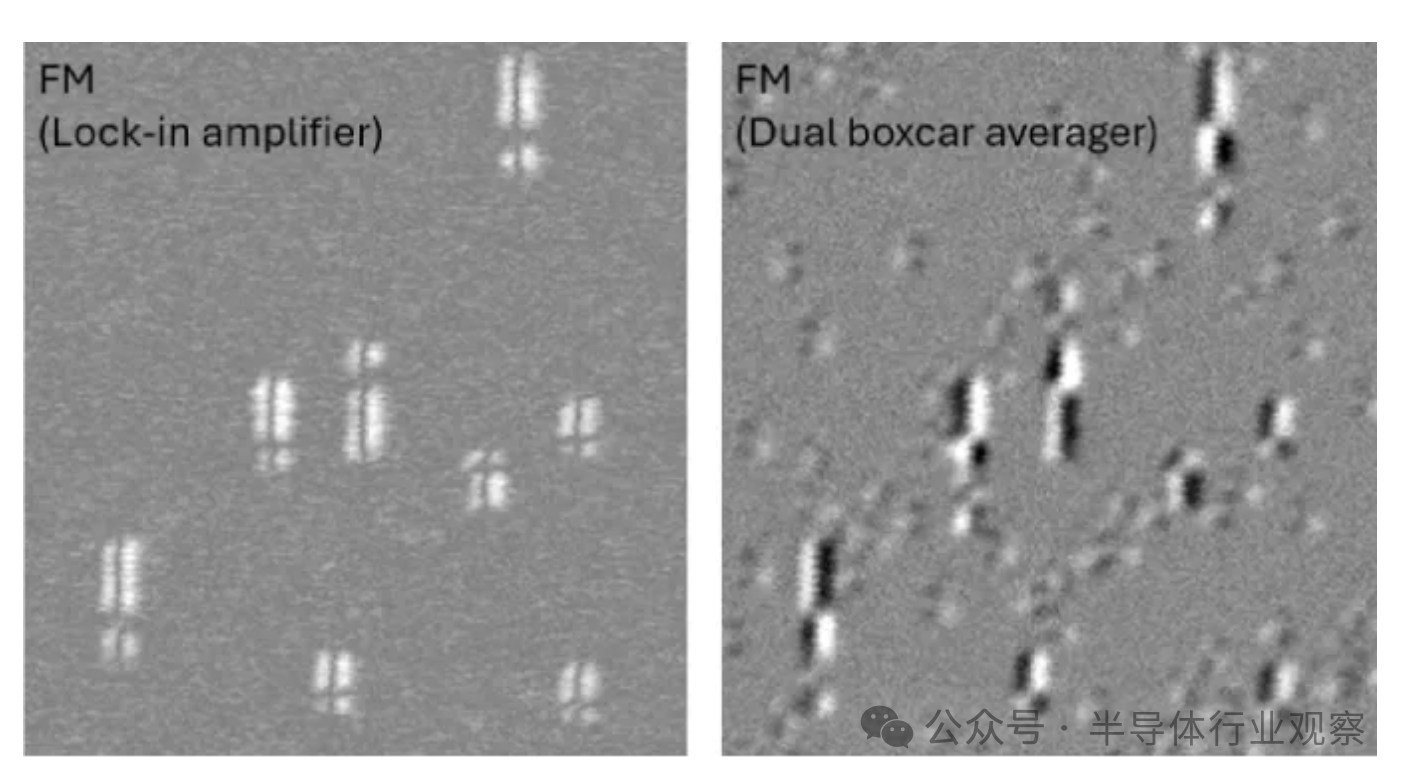

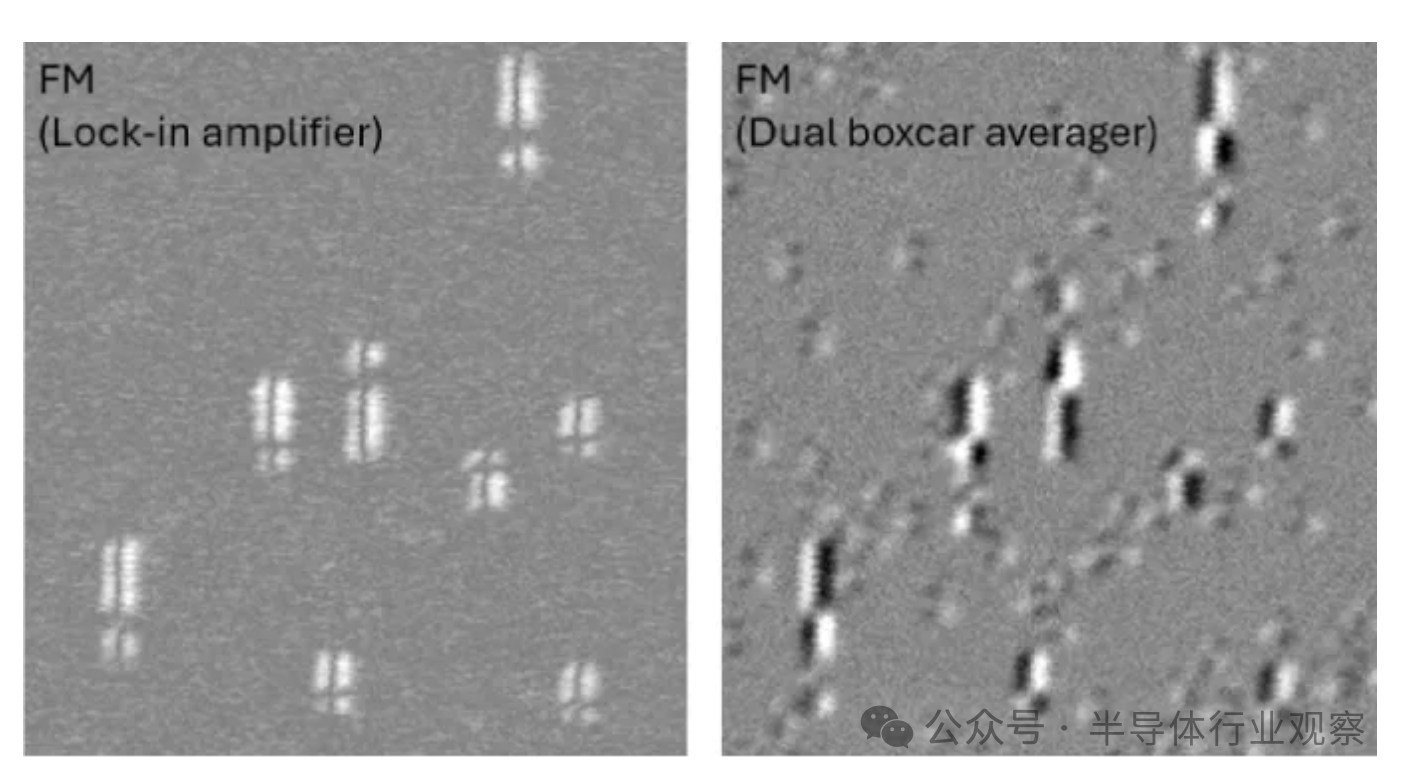

多维映射方案切换:在频域映射(FM)条件下,锁相放大器提供稳定的解调能力,适合快速扫描。而在复杂信号背景条件下,团队则切换至双 Boxcar 平均器,通过门控窗口提取目标信号时域分量。实验证明,Boxcar 模式在高平均次数下仍能保持高扫描速率,且得到的频域结果比传统方法更为丰富。

内部处理链路优化:团队在 FPGA 内部署了实时移动平均滤波器 。相比外接信号,基于内部低延迟互连构建的处理链路不额外引入噪声和传递失真。该滤波器算法在 312.5 MHz 时钟下运行,延迟仅为 224 ns,使信噪比(SNR)获得了约 16 倍的提升。

图 2:双Boxcar平均器得到的频域结果更为丰富

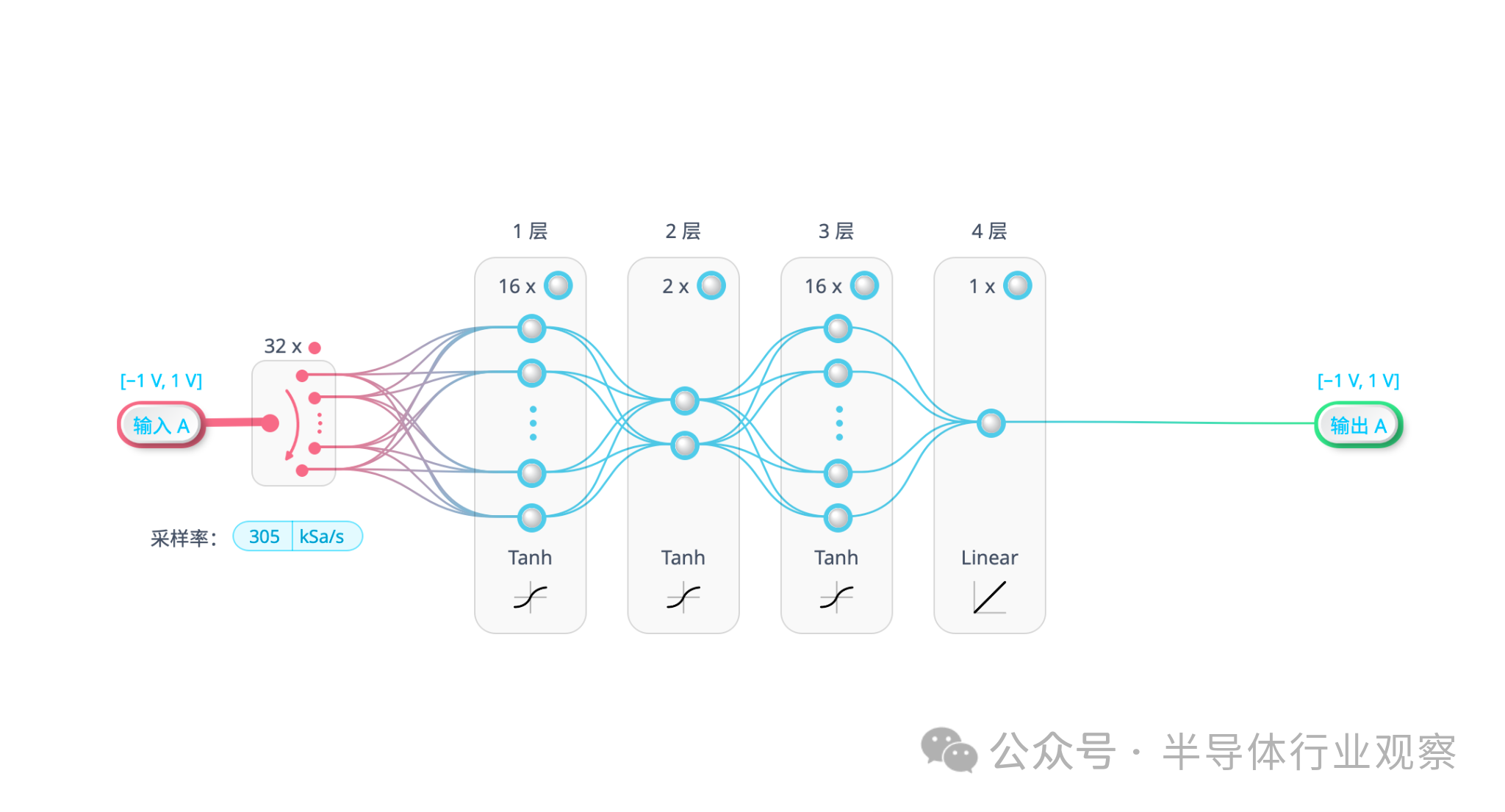

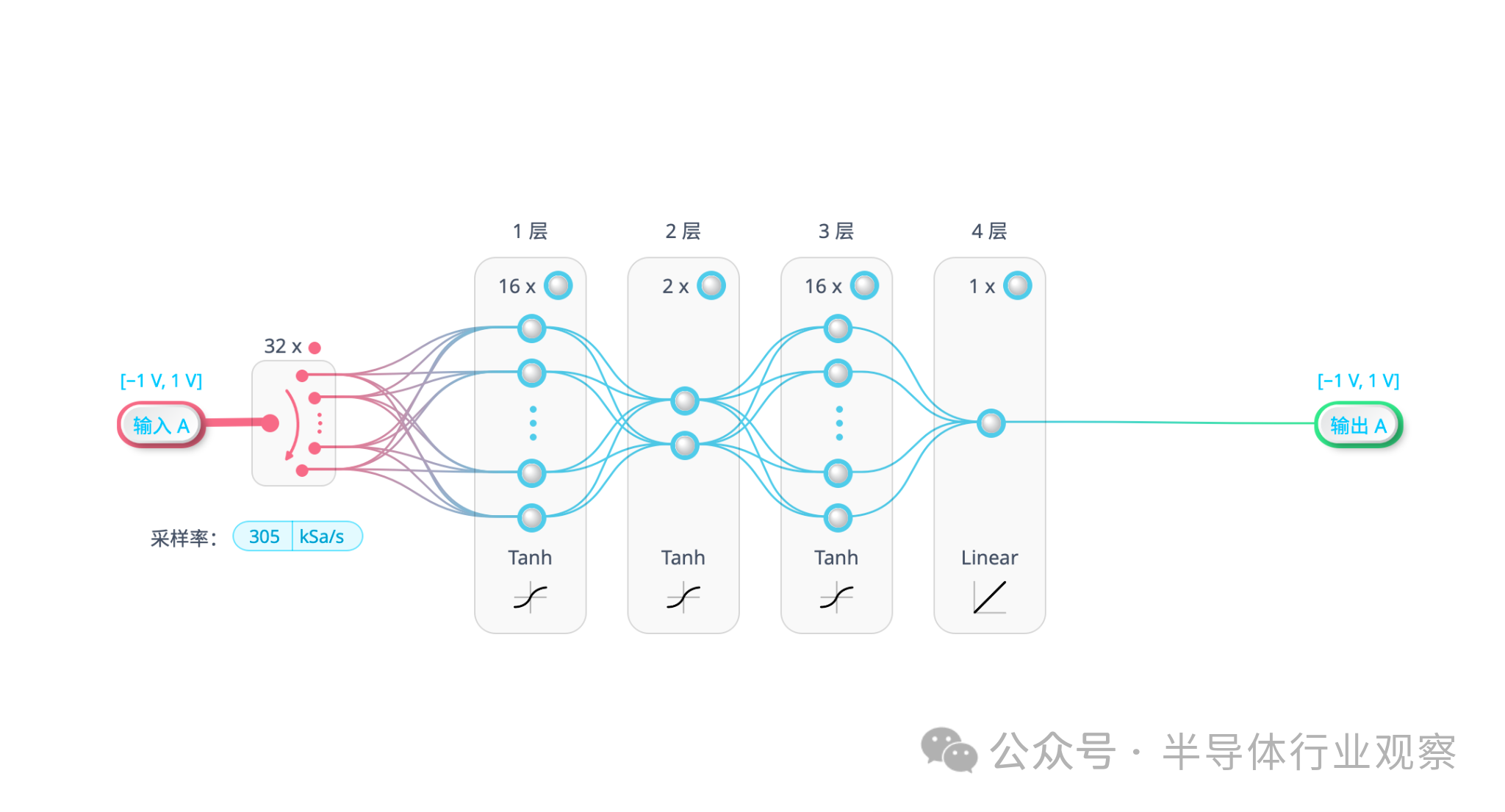

AI 赋能的信号重构:面对极限背景检测条件,Moku 基于 FPGA 的可重构架构支持将预训练的神经网络模型(如四层自动编码器 Autoencoder)直接作为在线处理模块部署到信号链路中。在满足实时性和算力资源的前提下,该系统实现了对目标信号的特征恢复与深度降噪,使得团队可以在不增加额外测量次数的前提下,提升缺陷判定的稳定性并改善整体测试效率。

这种将 AI 推理与精密测量深度融合的思路,不仅可拓展至更复杂的光学以及半导体故障定位技术,也为更广泛的失效分析与测试方法提供了新的实现路径。Moku 平台的功能不仅限于可重构仪器,更可作为满足多样化、特定化需求的定制化信号处理核心,持续推动测试测量领域的创新。

图 3:Moku 四层神经网络

结语:当器件复杂度提升,测试架构必须同步进化

随着硅光电集成和先进制造推动器件向更高集成度迈进,精准测控、实时反馈与动态调控能力已成为半导体企业的核心竞争要素。在上述案例中,我们清晰地看到了行业共同的演进趋势:测试系统不再依赖单一功能仪器的简单叠加,而是向系统层面的即时可重构能力跨越。

这种“可重构硬件+软件定义”的测试架构,正在成为高集成度芯片验证的重要方向。在这些前沿实践中,Liquid Instruments 基于 FPGA 开发的 Moku 平台提供了坚实的底座。利用 FPGA 强大的实时数字信号处理能力结合高速 ADC/DAC,Moku 实现了多仪器并行运行、实时信号处理以及内部数字互连。无论是在硅光芯片多维控制的并行优化,还是在量产阶段复杂背景下的信号提取,测试能力均能根据任务需求动态重构,并在同一硬件平台内完成采集、处理与反馈闭环。

Moku 单一平台内置多达 16+ 种仪器功能(如信号发生器、示波器、锁相放大器、PID 控制器等),具备 5 GSa/s 的采样速率以及高达 80 Gbps 的持续数据流输出能力。它支持多通道同步采集、实时信号处理与闭环反馈控制,大幅减少了多设备拼接带来的时序误差与系统复杂度。此外,单台Moku设备支持最多 8 个仪器槽位同时并行测试多个 DUT ,显著提升了测试速度,并从根本上降低了测试功能切换成本、布线难度及机架空间开销。面对 AI 与 CPO 时代,Moku 正在重新定义半导体测试的效率上限。

观展邀请

Liquid Instruments 将携 Moku:Go、Moku:Lab、Moku:Pro、Moku:Delta 全系列产品亮相慕尼黑上海光博会,展位号#N5.5702。展会同期,3月18日14:25,Liquid Instruments 首席执行官 Daniel Shaddock 将在“产业协同通信升级论坛”演讲并接受专访,分享公司在 AI 与测试测量硬件融合的最新突破成果。诚邀您莅临交流,共探 AI 协同智能测试新方向!

参考资料

1.NVIDIA, "Scaling AI Factories with Co-packaged Optics," 2025.

2.G. -L. Su, R. Kumar, D. Huang, D. Gold, R. Jones and H. Rong, "Heterogeneously Integrated III-V/Silicon C-Band Tunable Lasers on 300-mm Silicon Photonic Wafers," in IEEE Photonics Technology Letters, vol. 37, no. 20, pp. 1177-1180, 15 Oct.15, 2025

3.Zhi Hao Ko, Amitesh Kumar, Jobin Thomas Valliyakalayil; November 16–20, 2025. "Laser Probe Techniques withAdaptive FPGA Device." Proceedings of the ISTFA 2025. ISTFA 2025: Conference Proceedings from the 51stInternational Symposium for Testing and Failure Analysis. Pasadena, California, USA. (pp. pp. 129-135). ASM.

责任编辑:SemiInsights

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻