AI正在重塑芯片设计生产力:日观芯设发布RigorAI系统

2026-03-12

11:30:18

来源: 互联网

点击

2026年3月12日 —— 近年来,芯片设计复杂度和成本呈指数级增长,SoC芯片设计涉及数十款EDA工具和数百个工程步骤,而芯片指标不断要提高,上市周期逐步压缩。在此背景下,传统依赖手动调优与工具驱动的设计模式正逐渐接近效率瓶颈。

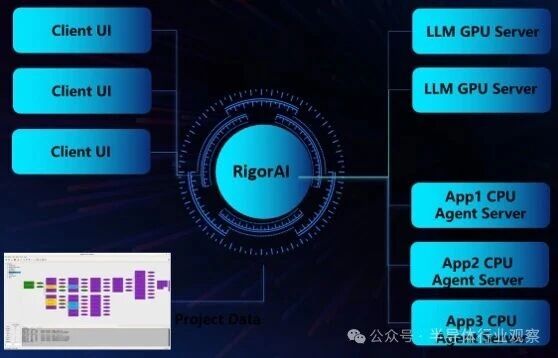

近日,专注于数字电路设计与优化的EDA企业日观芯设正式发布其AI驱动芯片设计系统 RigorAI。该系统通过融合大模型技术、智能体系统与自动化工作流,构建新一代AI驱动的芯片设计平台,显著提升设计效率与工程生产力。

三年布局,为弯道超车打下基础

新年伊始,AI自动化芯片设计的概念在全球受到高度关注,美国Ricursive公司刚成立两个月就获得40亿美元估值,显示出行业对这一方向的巨大期待。

然而早在三年前,日观芯设已开始围绕芯片工作流程自动化、芯片数据分析、提取与管理进行布局,并陆续推出 RigorFlow工作流管理、Rigor系列签核分析工具等产品。这些产品为AI能力的引入奠定基础。相关产品早已在多家企业落地应用,并获得客户积极反馈。

日观芯设CEO林逸舟博士表示:“日观前期开发的流程工具和数据系统,是为AI能力准备数据燃料。我们起初是为深度学习类AI准备的,随着近两年LLM技术的突飞猛进,我们的产品路线与AI技术演进高度契合。这里有前瞻的规划,也有幸运的成分。在多年打造的产品基础上,RigorAI系统的目标是让AI成为芯片企业的‘超级助手’,为设计流程的各环节提供决策支持和自动化能力。”

为芯片设计场景精心打造

RigorAI系统由工作流平台(Workflow),智能体和知识库平台(Agent)、和芯片数据平台(Database)三部分组成。智能体作为新兴事物,在安全性、稳定性和可控性方面有很多不足,目前风靡的OpenClaw就暴露出很多隐患,RigorAI系统在设计之初便充分针对芯片企业场景,在数据安全、权限管理和系统稳定性上为用户考虑。系统支持企业级私有化部署,并构建了完善的安全控制机制,配合企业驾驭AI生产力。

RigorFlow:高效率驾驭智能化工作流

如果说大模型是芯片设计的“大脑”,那么自动化工作流就是执行任务的“双手”。RigorAI工作流系统能够自动调度EDA工具、运行设计流程并生成分析结果,使工程师无需再频繁修改脚本或手动管理任务。通过自动可视的流程管理,一个工程师能够同时驾驭的设计流程数量,从过去的两三个提升到几十个,显著提升效率。

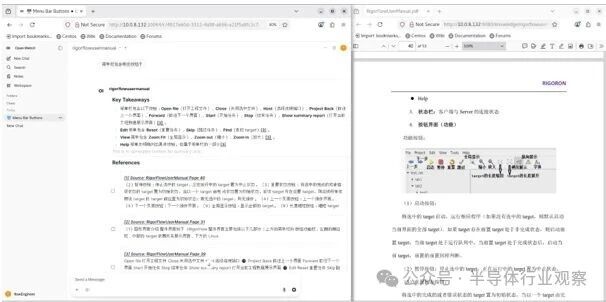

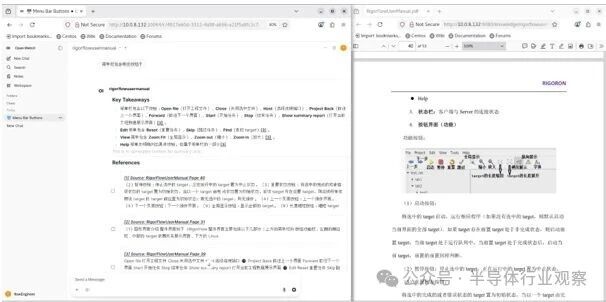

RigorAgent:全方面助力设计步骤

Agent平台不仅打造多种专业智能体,例如PR优化智能体、FP智能体、DRC修复智能体等,企业用户还可以根据自身需求,自主构建多智能体协作体系,使AI能够自动处理复杂设计任务。

Agent平台不仅打造多种专业智能体,例如PR优化智能体、FP智能体、DRC修复智能体等,企业用户还可以根据自身需求,自主构建多智能体协作体系,使AI能够自动处理复杂设计任务。

平台还为工程师打造EDA工具专家知识库,针对芯片设计问题提供无幻觉的专业回答,自动构建持续演进的企业级私有知识库,大幅减少人工查阅文档和排查问题的时间。

RigorDB:智能化设计的数据底座

数据既是管理决策也是AI驱动的核心基础,RigorDB是一个面向芯片设计工作流的智能数据库系统,它统一管理芯片的层次化数据、版本、工作流中的日志等,给项目管理人员提供自然语言查询的多种能力,比如自动化提取,多维度分析,可视化图表展示等,为决策提供灵活的数据支持。

数据既是管理决策也是AI驱动的核心基础,RigorDB是一个面向芯片设计工作流的智能数据库系统,它统一管理芯片的层次化数据、版本、工作流中的日志等,给项目管理人员提供自然语言查询的多种能力,比如自动化提取,多维度分析,可视化图表展示等,为决策提供灵活的数据支持。

助力国产生态

RigorAI系统深度融入国产半导体生态,不仅服务国内多家芯片设计企业,而且在自身搭建上也与国产生态紧密相连,形成一个开放的平台,系统既与国产GPU适配提效,又积极支持国产EDA工具的集成调用,成为自主可控的芯片生态的一份子。

关于日观芯设

日观芯设成立于 2021年,是一家专注于芯片设计全流程智能化的国产EDA企业,致力于通过AI技术重塑芯片设计生产力。公司汇聚元禾璞华、创维投资等多家产业资本,创始人及核心研发团队拥有20余年EDA研发经验,持续推动国产EDA技术的发展。

责任编辑:SemiInsights

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻